Other Parts Discussed in Thread: UCC25800-Q1

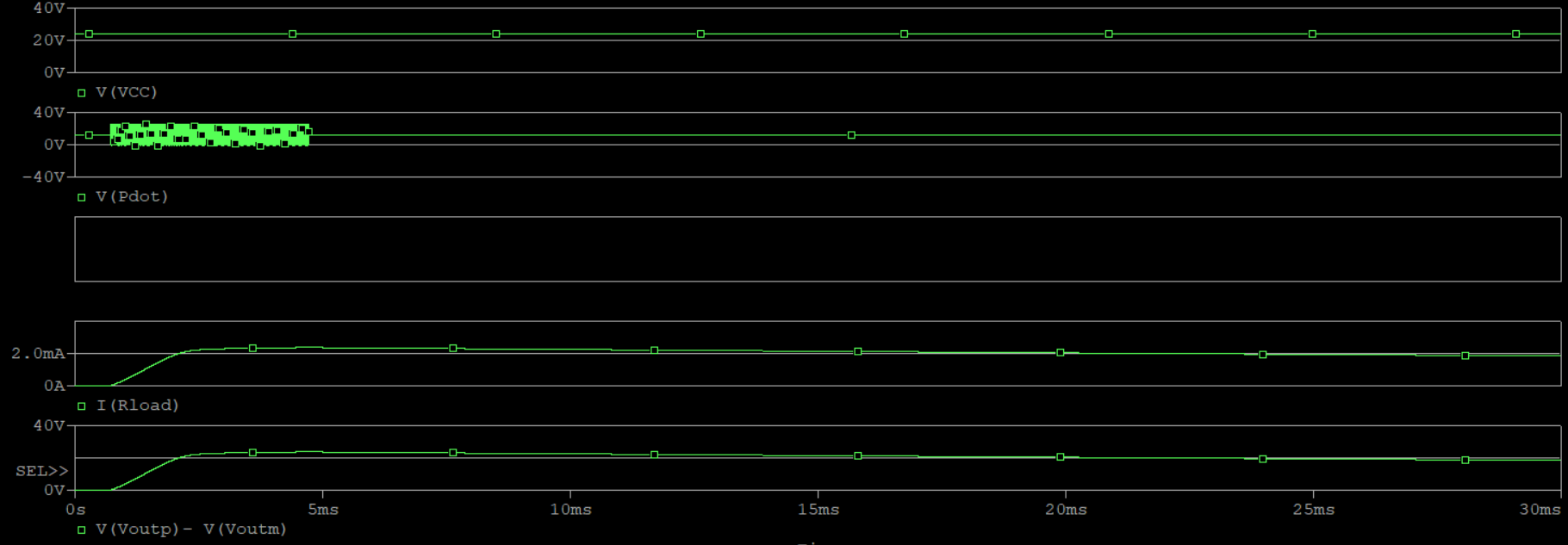

在仿真过程中,我们发现UCC25800的DIS_FLT_N在仿真5ms后从高电平5V掉到了低电平0V,同时SW引脚也停止工作。

我们查看了其它引脚的电平,没有出现抖动或者掉落的情况。请问什么情况下会触发DIS_FLT_N的报错?我要怎么样排查故障?

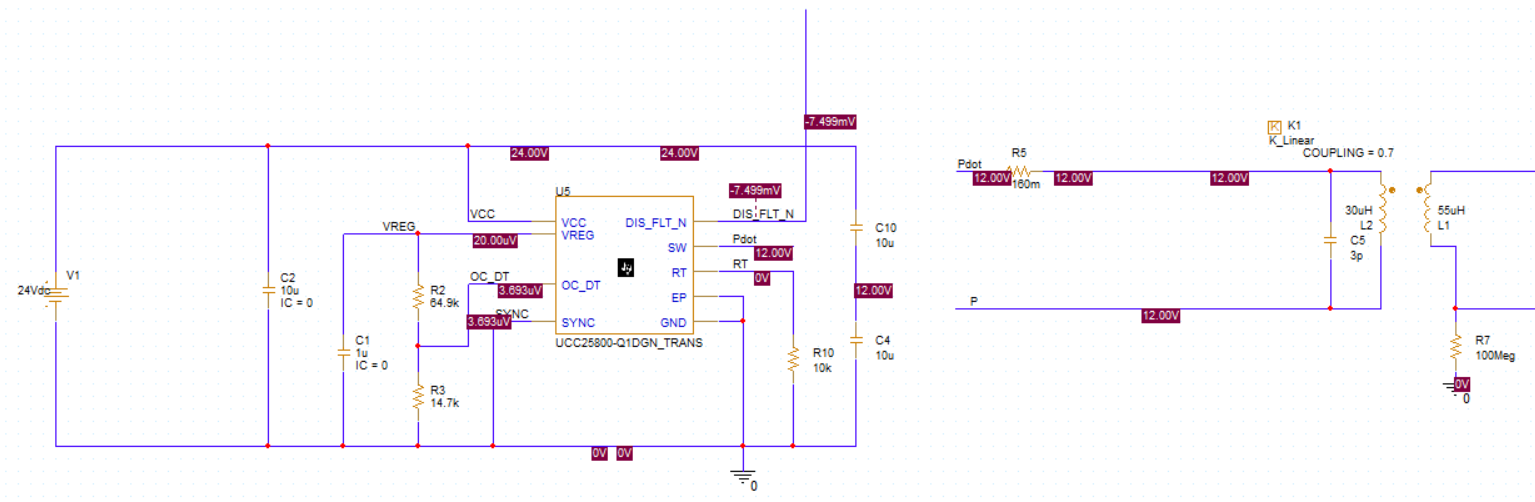

下图是我的仿真结果和仿真电路。

在仿真过程中,我们发现UCC25800的DIS_FLT_N在仿真5ms后从高电平5V掉到了低电平0V,同时SW引脚也停止工作。

我们查看了其它引脚的电平,没有出现抖动或者掉落的情况。请问什么情况下会触发DIS_FLT_N的报错?我要怎么样排查故障?

下图是我的仿真结果和仿真电路。

DIS/FLT引脚是一个输入/输出引脚。可以是

外部驱动以启用或禁用变压器驱动

读取作为状态标志,告诉变压器驱动器是否处于故障模式,具体是什么故障,如数据表第8.3.6.1节故障代码所述。

左浮动以默认启用变压器驱动程序

内部引脚是绑高通过100-kΩ从VREG上拉电阻。这个上拉电阻只有在VREG引脚高后才激活。如果UCC25800-Q1变压器驱动器进入故障模式,DIS/FLT引脚通过750µa电流源内部拉低。当引脚低时,开关被抑制。

一旦VCC电压超过UVLO上升阈值,DIS/FLT内部下拉电流源在上电过程中被激活。在VREG电压上升到VREGOK阈值以上后,下拉电流源被释放,DIS/FLT引脚上升(除非它被外部拉下)。当DIS_FLT_N将其状态从5V更改为0V时,请检查VCC/Vreg值

当DIS/FLT引脚电压超过ENTH阈值时,变压器驱动使能。当DIS/FLT引脚低于DISTH时,变压器驱动器被禁用。如果担心DIS/FLT引脚的噪声耦合,可以使用外部电阻将其拉到外部导轨或VREG。为了读取引脚作为状态标志,外部电阻值必须足够高,以便750µa电流源可以将引脚拉到低于读取引脚的设备的阈值水平。为了将引脚读取为故障输出,建议外部上拉电阻5v的值为10 kΩ。

如果不需要DIS/FLT引脚功能,它可以保持浮动或绑定到VREG,以允许变压器驱动器正常工作。虽然我不能在你的原理图中清楚地看到它,我认为你已经把你的VREG直接绑在DIS_FLT引脚上,试着保持它浮动并测量VREG。

此外,如果您确实在原理图中的其他地方加载VREG引脚,请了解该引脚的过载保护功能。测量VREG上的电流负载

为了防止VREG引脚过载,VREG引脚自带过流保护。在启动过程中,当VREG引脚电压低于1v时,VREG引脚电流被限制在15ma,以保护IC免受短路或过载的情况。当VREG引脚电压高于1v时,VREG引脚电流限制增加到40ma,以实现快速启动。当电压超过VREGOK值时,VREG引脚电流限制返回到15 mA。由于VREG引脚为内部电路和外部电路提供电流,因此建议将VREF引脚的外部负载保持在1ma以下。当外接VREG引脚电流在1ma ~ 15ma之间时,过大的VREG引脚电流会导致VREG引脚电压下降。在正常工作期间,如果VREG引脚过载并且其电压降至VREG低阈值以下,则变压器驱动器关闭线性稳压器并进入锁存模式。