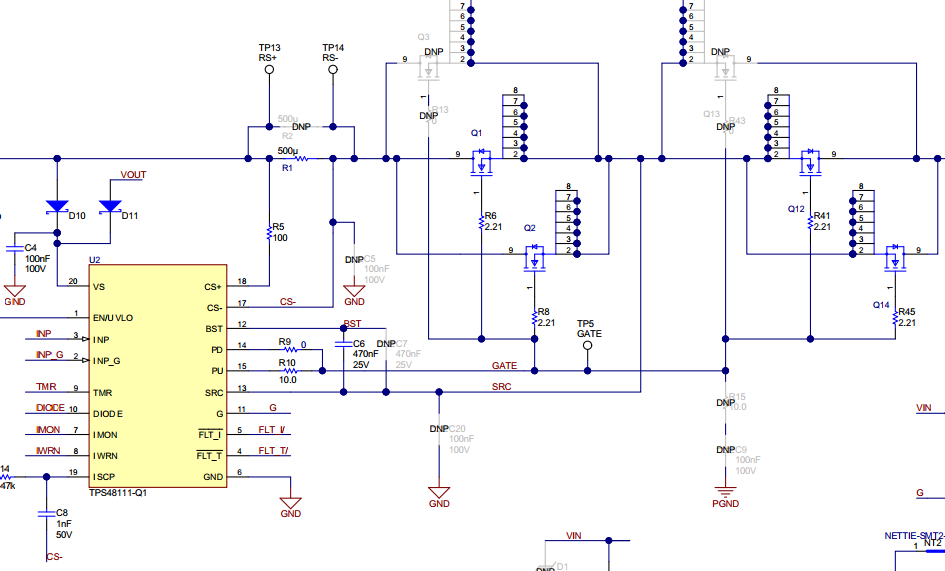

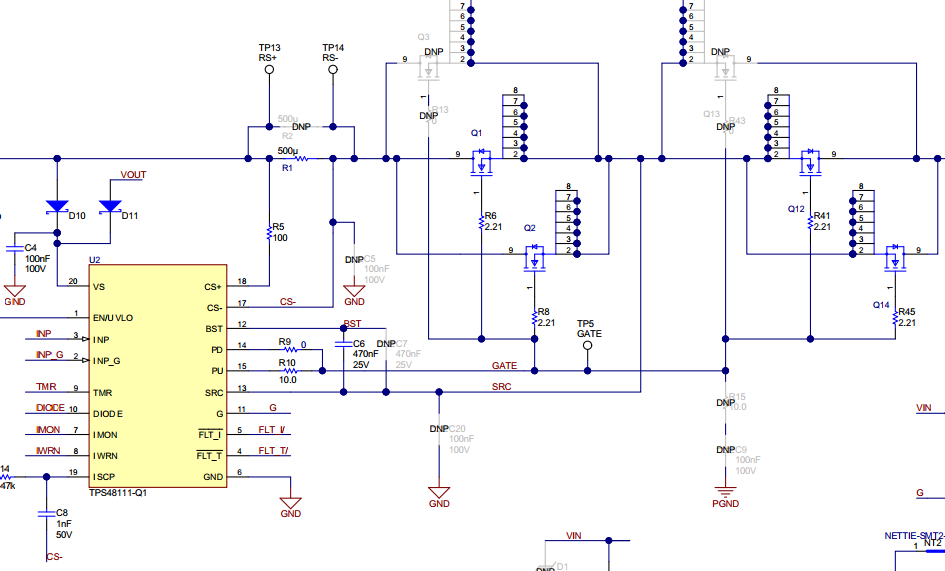

如下图所示:只有1对Q1,Q12 MOS管时,可以正常驱动开关;当并联Q2,Q14时,mos不能打开,pd/pu输出0。请问这个大概什么原因?谢谢!

mos管Qg约230nc,4个mos并联时,Cbst大概需要1uf电容。

当前Cbst是1uf, 修改成3uf也同样情况,不能驱动2对mos。

如下图所示:只有1对Q1,Q12 MOS管时,可以正常驱动开关;当并联Q2,Q14时,mos不能打开,pd/pu输出0。请问这个大概什么原因?谢谢!

mos管Qg约230nc,4个mos并联时,Cbst大概需要1uf电容。

当前Cbst是1uf, 修改成3uf也同样情况,不能驱动2对mos。

对于 EVM,Q2 和 Q14 默认是已安装的。你没法开箱即用地让它工作吗?还是在你移除 Q2 和 Q12 并尝试重新安装后,它就不再工作了?

既然你报告 PU/PD = 0V,你能确认 INP = 高电平且 FLT = 低电平吗?

感谢回复!我是参考这个evm原理图重新制作的板,出现上面的情况。PU/PD对GND约 -0.7v,SRC对GND约 -0.7v。INP是高电平5v,FLT也是高电平5v。DIODE引脚目前是短路接GND,因为当焊接NPN 3904三极管后,tps48111器件pu/pd输出0,FLT_T输出低电平报警。

芯片供电VS引脚的D10短路,D11没有。INP_G默认下拉,没有使用预充功能。输入电压30-50v。目前测试输出是5欧电阻负载,没有大容量电容。

非常感谢您提供的所有细节。对于一个纯电阻5欧姆的负载,您只需拉取约10安培的电流,这对该设备来说非常简单。

如果FLT保持高位且您的INP为HIGH,Gates应无任何问题。

能否请您提供包含Vs、Pu/PD、SRC、BST及+BST-SRC的波形?

你是否已在多块板上确认过这种情况?请再次检查你的焊接工作,确保场效应晶体管已正确安装。使用>1uF的去耦电容应该没有问题。

第1张图中Vs对地波形标注有误,不是芯片的Vs引脚对地,而是SRC引脚对地的波形。