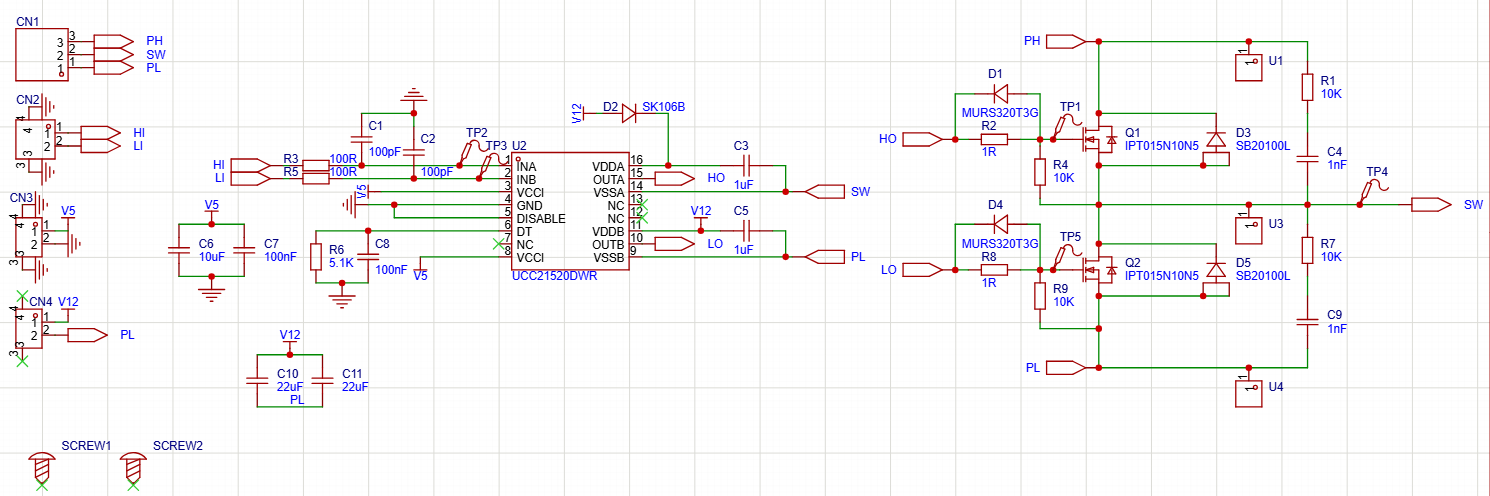

Part Number: UCC21520

参考UCC21520数据手册绘制半桥栅极驱动,但出现较为严重的振铃现象,且二次布局布线后无明显优化效果,请求帮助

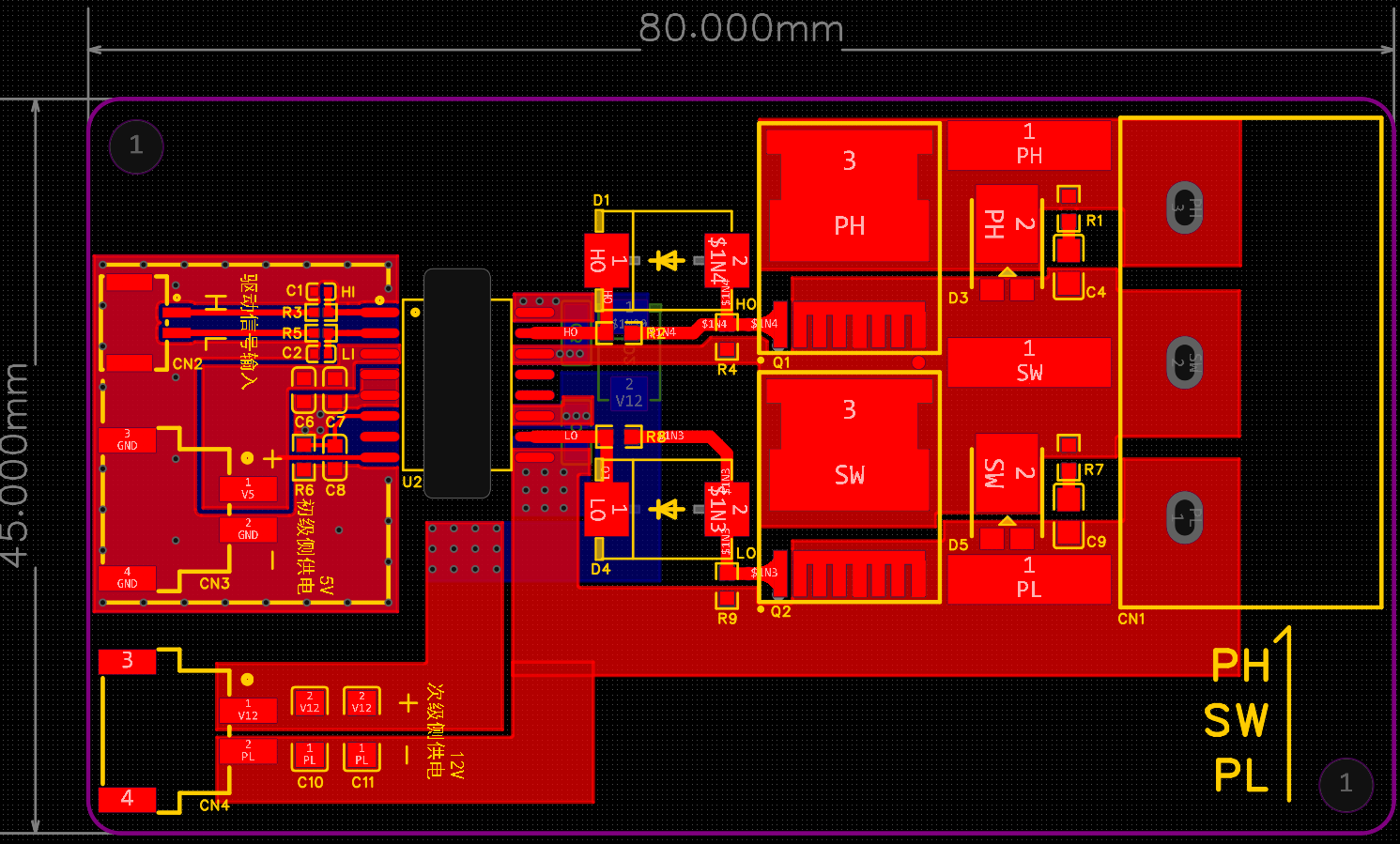

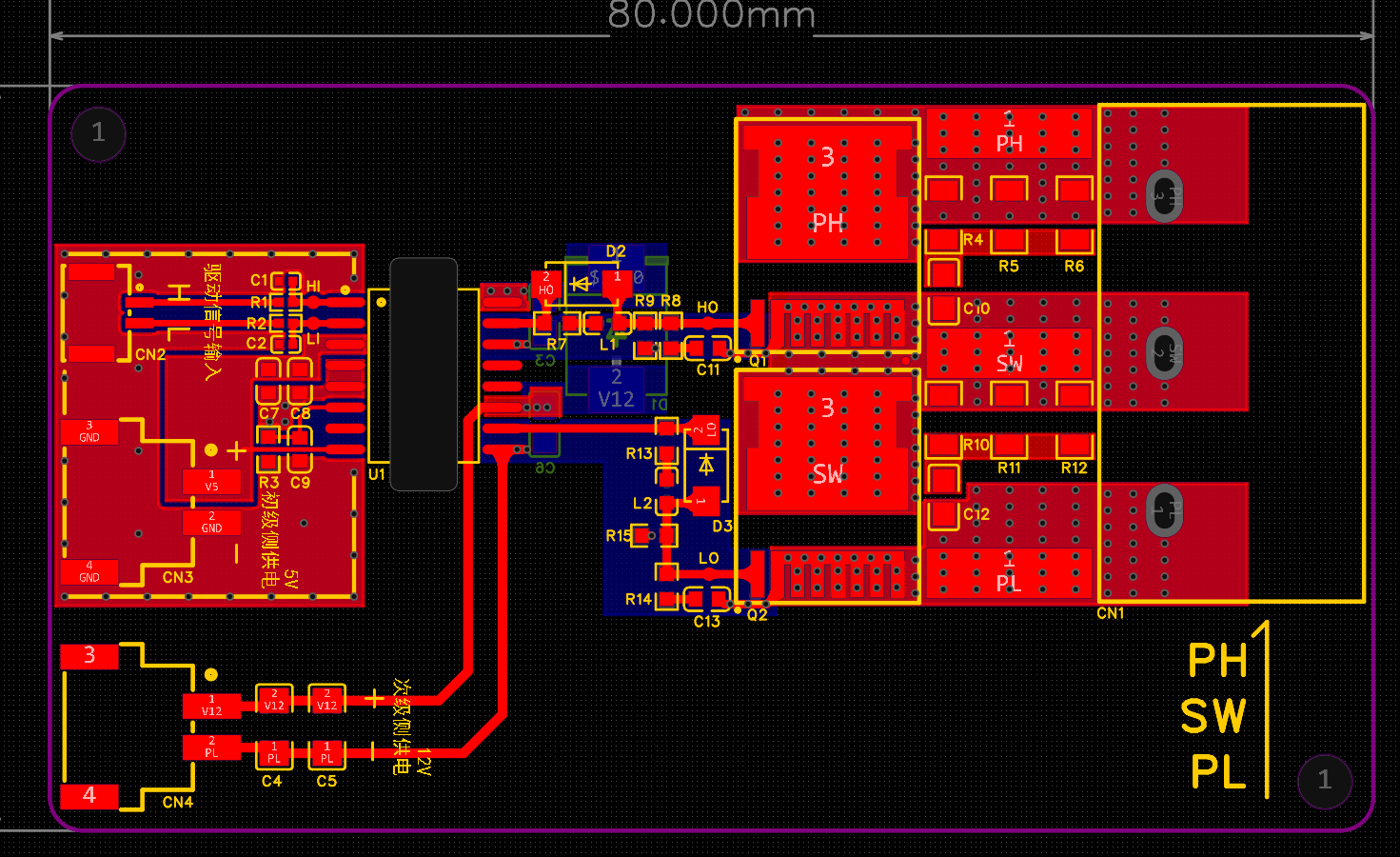

1.第一版Layout与测试波形

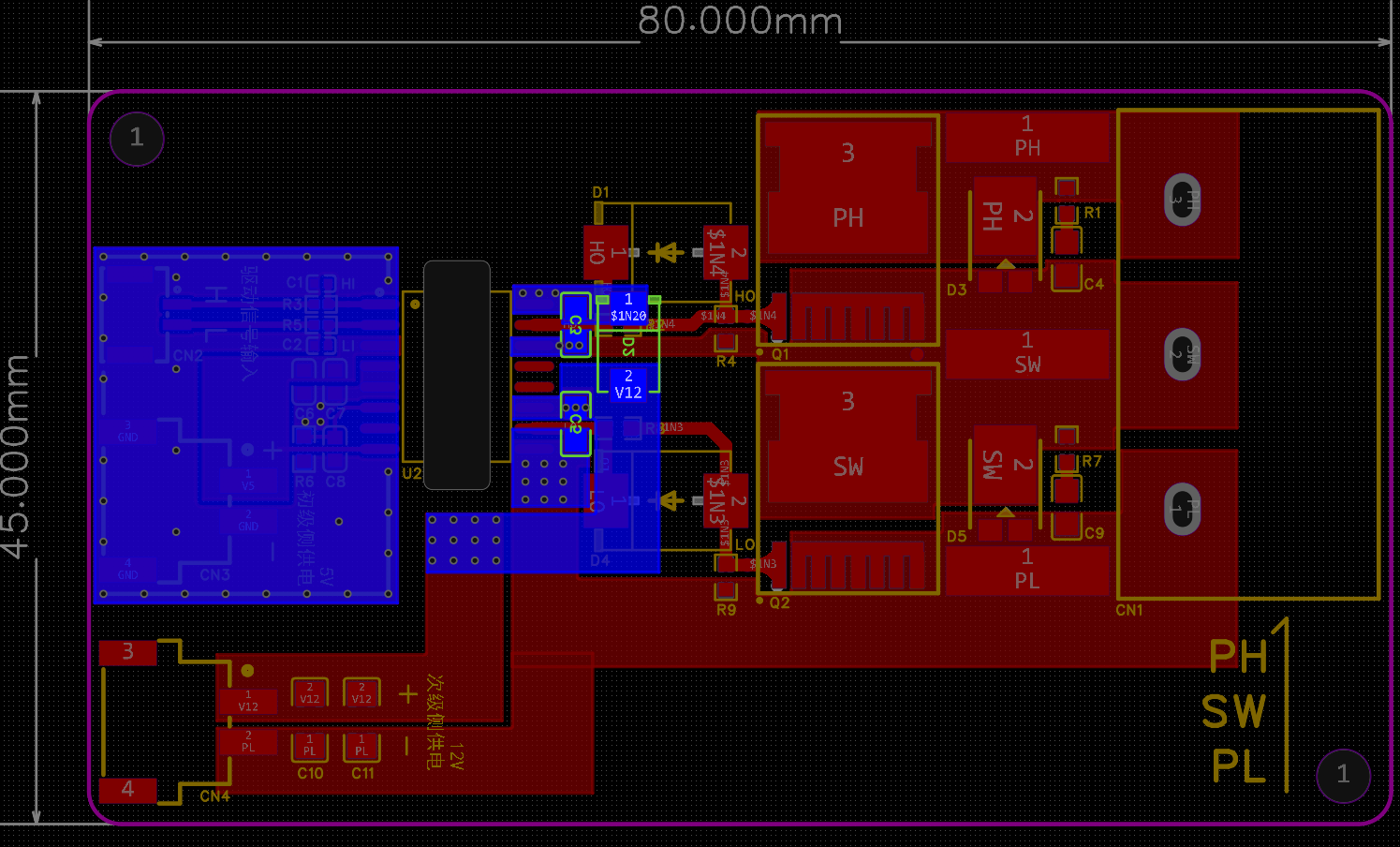

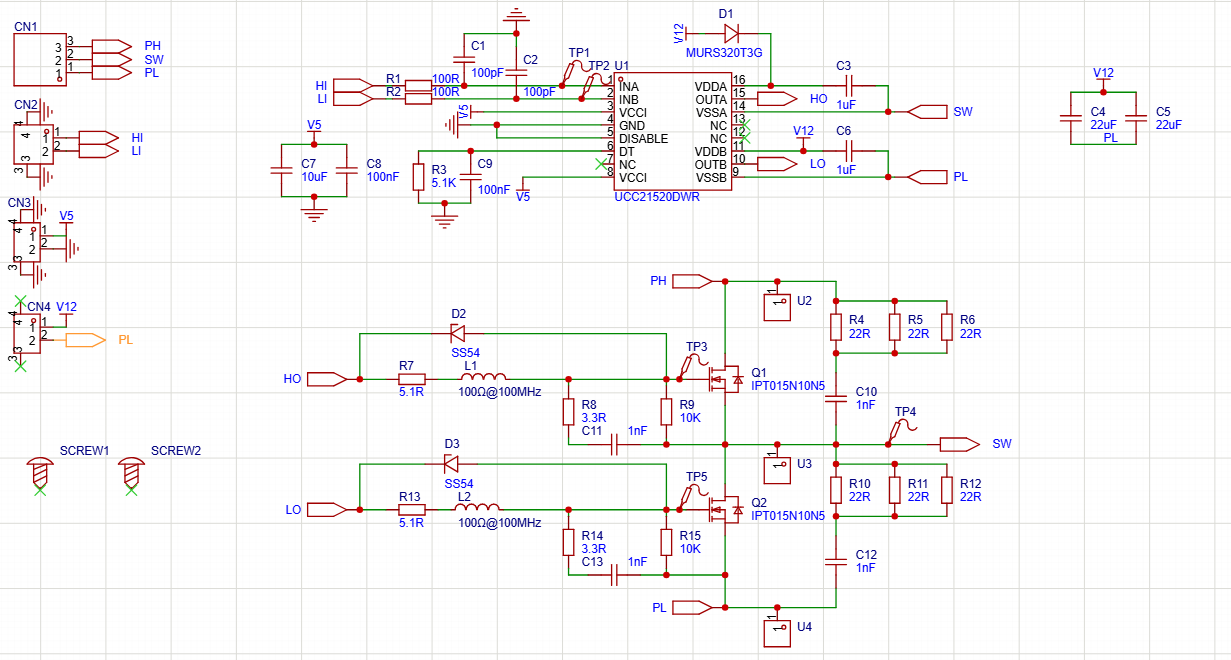

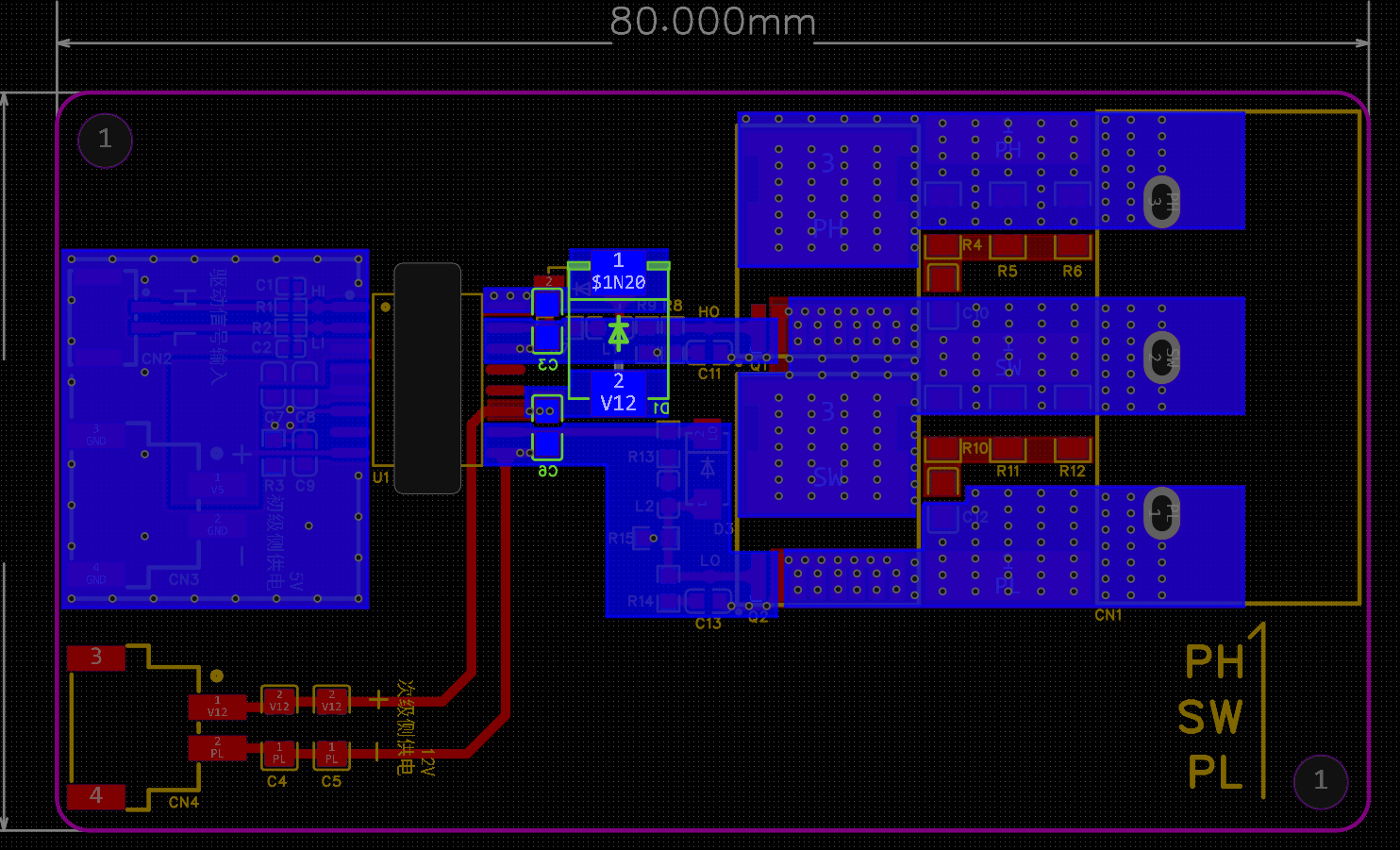

2.第二版设计与测试波形

由于考虑到磁珠在低频下体现电感性,在实际焊接时采用3.3R电阻替代

I would recommend minimizing the gate drive loop as much as possible to limit ringing from inductance. I can't tell how long the gate drive paths are, but I would analyze if these can be shortened in the next layout revision.

I also wonder if there is ringing in the switched node. It's impossible to see without seeing scope shots of this. This would be the easiest thing to check. In order to mitigate switched node ringing, I would recommend adjusting the gate drive resistors (increasing them) in order to slow the turn on and turn off time of the FETs, which will slow the turn on and turn off time of the switched node, preventing it from ringing. This is somewhat of a low-efficiency solution. You could also add a ferrite bead that presents a high impedance at this resonant frequency, but low impedance to the <20MHz gate drive current transients.

Finally, if you would like to do an in-depth and detailed schematic review for each component, then I would recommend to use this Application Guide [Link], which will help address each of the necessary components for the schematic review.

I would recommend only adjusting one part of the schematic at a time, so that you can identify what components are making a difference, and which components are not needed. Please feel free to send scope further scope captures of this problem and we can dig into it.