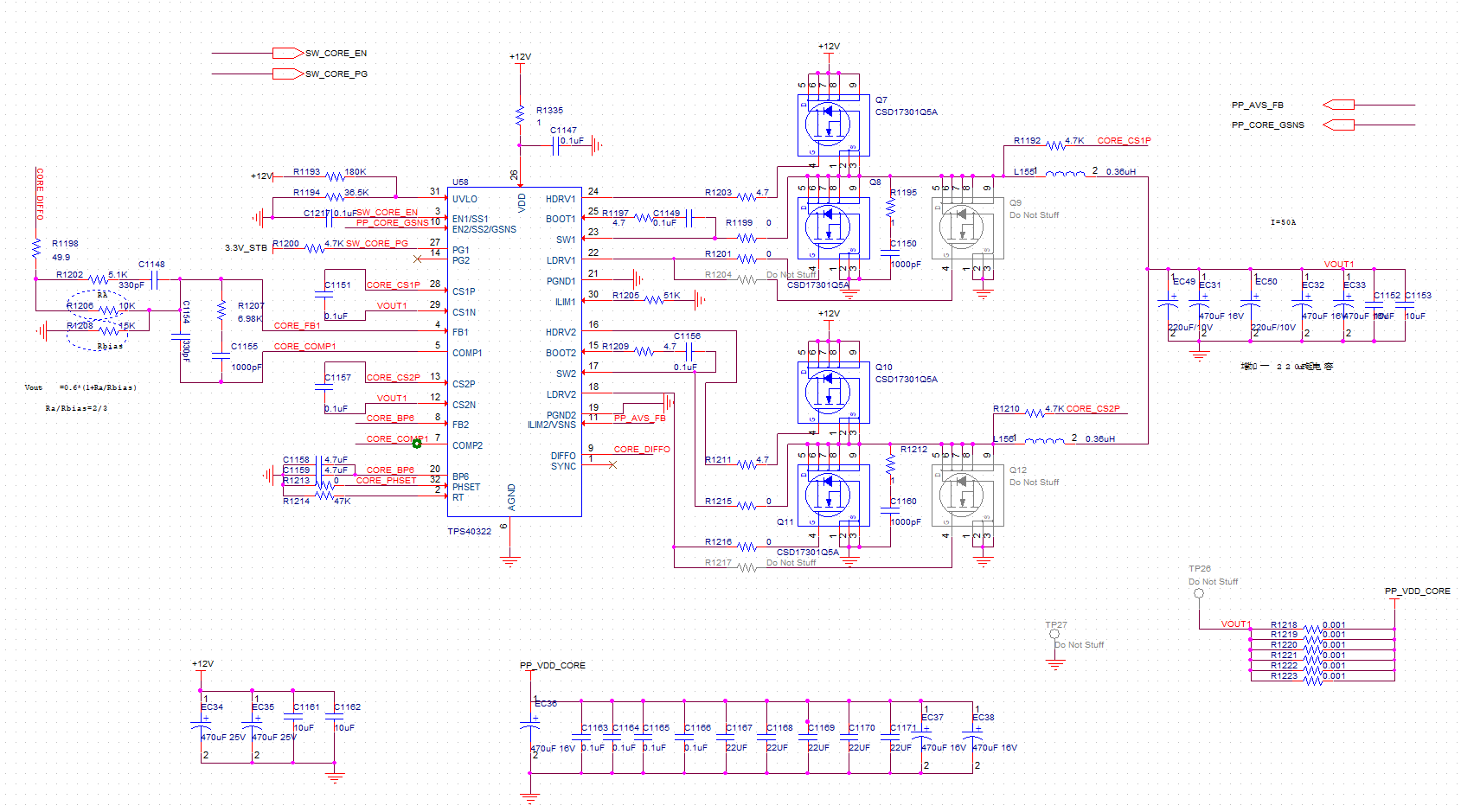

量产单板,TPS40322 + csd17301q5a (上/下管同型号),双相,预期满载输出3.3V/30A,但在生产过程中约5%比例出现MOS管击穿(故障板上电1分钟~2小时不等,没有特定时间),出现故障时3.3V轻载仅2~3A。

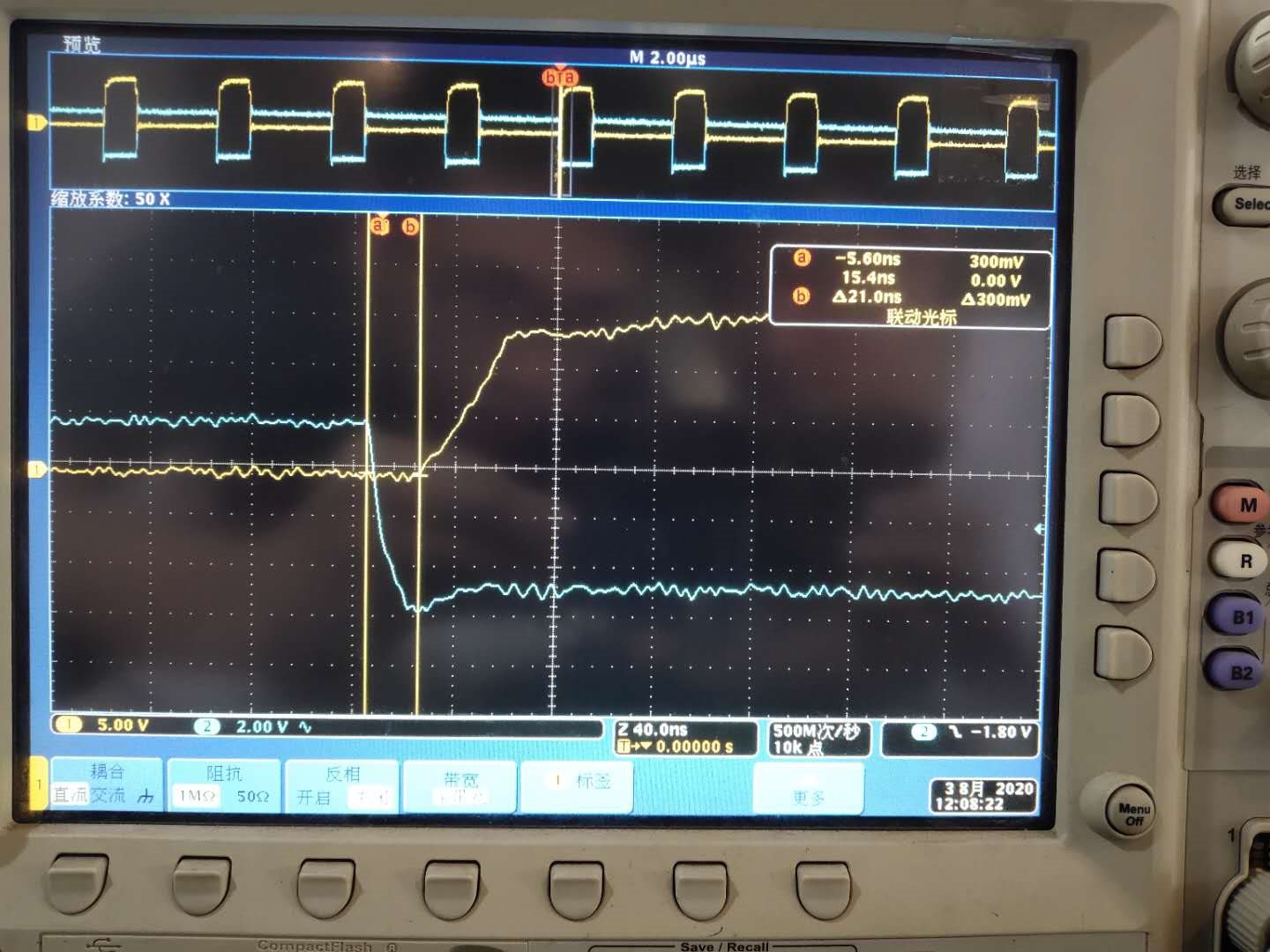

重新核对参数,发现TPS40322 PWM的死区时间为 20~40ns,并且,L fall H rise的边沿,用示波器测量死区时间21ns,接近下限值。那么,查看芯片及MOS管参数,计算延迟:

Tlfall + Td_off + Tf = 10 + 28 +10.5 = 48.5 ns (下管关闭)

Tdead + Td_on + Tr = 20 + 10.7 +16.2 = 46.9 ns (上管导通)

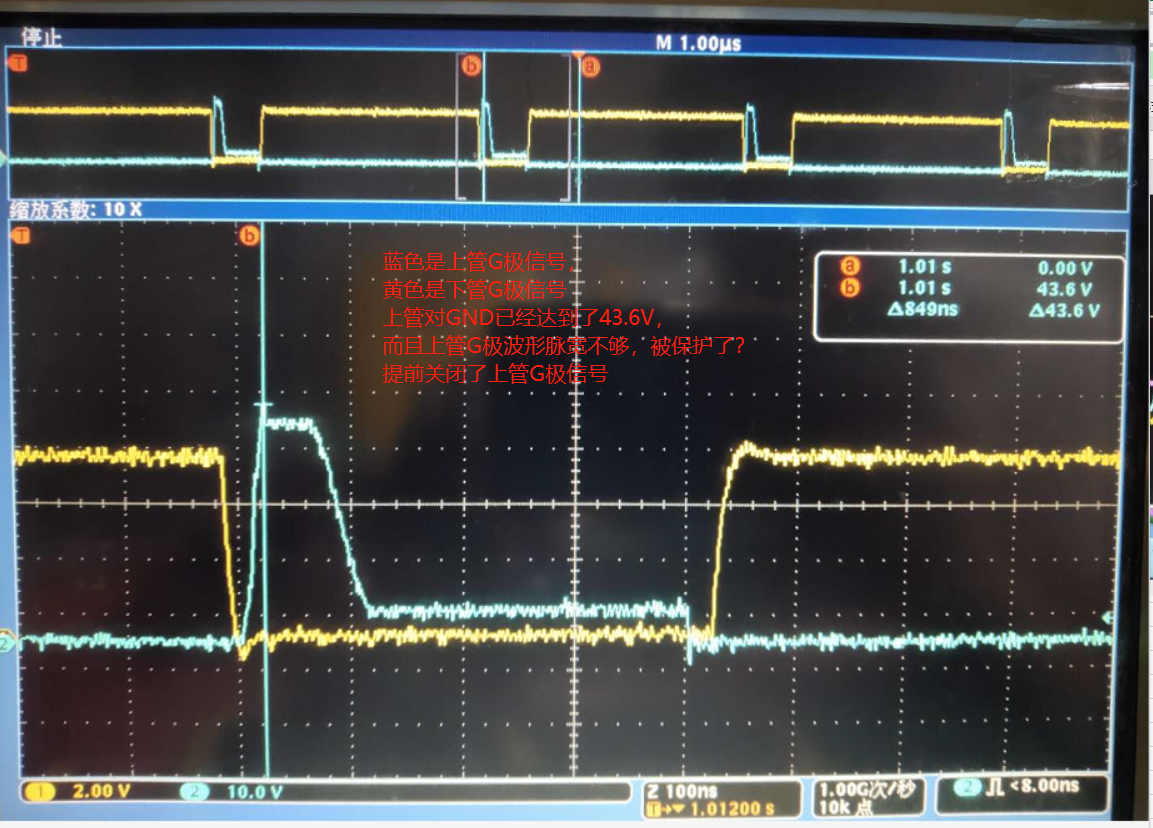

这是不是意味着,在下管尚未完全关闭时,上管已经导通了 ?这个计算方法正确吗?