Hi,

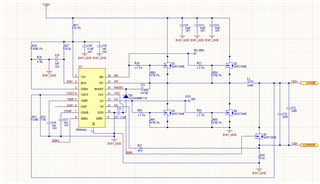

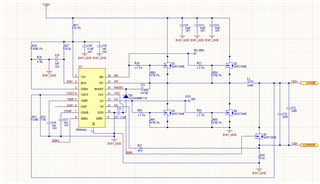

设计了一个36V输入,24V 1~8A输出多LED串并的驱动电路,原理图参照官方设计

开关频率设置为:416K左右

电感选用的18A饱和电流

当前未外接负载,IADJ输入为0.15V,理论上此时采样电阻上电流为1.5A

问题:

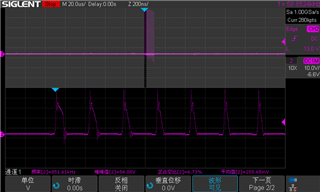

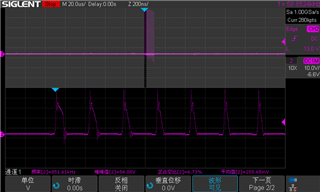

1. 虽然是空载,HG,SW,LG上的开关波形非常杂乱,尖峰过大,局部都超过FET的Gate耐压了

LG波形

HG上波形

这种情况一般是什么导致的呢?

Byron

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

设计了一个36V输入,24V 1~8A输出多LED串并的驱动电路,原理图参照官方设计

开关频率设置为:416K左右

电感选用的18A饱和电流

当前未外接负载,IADJ输入为0.15V,理论上此时采样电阻上电流为1.5A

问题:

1. 虽然是空载,HG,SW,LG上的开关波形非常杂乱,尖峰过大,局部都超过FET的Gate耐压了

LG波形

HG上波形

这种情况一般是什么导致的呢?

Byron

Hi

建议你先通过Vadj或CS电阻设置LED电流在1A内,并先驱动单个MOS, 让LED先正常工作起来。(从你描述看,noise很大,可能和layout有关,电流小些,layout的影响也会小些)

测试时不可以空载,原因是LED是恒流设计,空载会导致输出duty增大而OVP保护。