Other Parts Discussed in Thread: UCC21710,

对于 SiC 驱动,我们需要缩短短路检测时间!

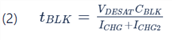

该值由消隐电容器的容值和内部 DESAT 充电电流固定值 (500uA) 决定

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

具有 DESAT 检测功能的栅极驱动器通常使用 IGBT 进行短路检测。使用集成 DESAT 的栅极驱动器进行设计时的一个限制是,通常很难实现足够短的 SC 检测时间,因此我们可以在发生损坏之前(在几微秒内)关闭 SiC FET。这个时间比使用 IGBT 时的时间短得多,IGBT 通常具有 10us 的短路耐受时间。

为 SiC FET 定制 DESAT 检测的一个关键挑战是,需要使用容值大于 100pF 的消隐电容器来提供强大的防误报保护并保持可靠的检测。

在具有 DESAT 引脚 (500uA) 的器件中,为消隐电容器充电(从而设置消隐时间)的内部充电电流是固定的,因此我们控制消隐时间的主要方法通常是更改电容值!高功耗应用的性质意味着,瞬态可能会通过 DESAT 电路中的 HV 阻断二极管耦合并导致误报检测,因此不推荐选择容值非常小的电容器。

这是具有 DESAT 引脚的器件(UCC21710、UCC21750/59 和 ISO5x5x 系列)面临的挑战。具有 OC 引脚的器件可配置为 OC-for-DESAT(有时称为“伪 DESAT”),不具有此限制,因此非常适合 SiC 应用。OC-DESAT 允许设计人员任意设置 DESAT 检测阈值和 td

但是,通过简单地修改典型电路,我们还可以为具有 DESAT 引脚的器件添加另一个消隐电容器充电电流路径。

这样,我们便可以实现更快的短路检测,有效地保护 SiC FET,而无需选择容值很小的消隐电容器,从而不必在检测时间和 SC 保护电路可靠性之间进行权衡。

另一方面,调整 DESAT 检测阈值(E2E 常见问题解答)也可以缩短检测时间。

本文档提供 PDF 格式,链接如下

Increase_DESAT_Charging_Current_E2E_public.pdf

UCC2175x 和 ISO5x5x 通过集成式 DESAT 检测进行短路检测和保护。DESAT 系统有一个内部电流源,该电流源为外部电容器充电,从而设置“消隐”时间以防止误报。在某些情况下,设计人员可能希望提高消隐电容器的充电电流,以缩短从故障到关断的时间。这在驱动 SiC 时至关重要,因为它们的额定短路耐受时间比 IGBT 短得多。消隐电容器的容值也可以更小,但不要太小,因为消隐电容器有助于抑制 DESAT 引脚上的噪声。

与使用带有 OC 引脚的 UCC217xx 变体实现 OC-AS DESAT 类似,我们可以使用外部元件补充 UCC2175x 和 ISO5x5x 中的内部 DESAT 电流源。

有关短路检测方法的更多详细信息,请参阅我们的电子书《IGBT 和 SiC 栅极驱动器基础知识》。

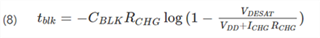

在正常运行期间,内部电流源 ICHG 通过串联电阻器和 HV 阻断二极管流向集电极,如图 1 所示,其中 VBLK 是消隐电容器 CBLK 上的电压和 DESAT 引脚上的电压。因此,该电压低于内部 DESAT 检测阈值 VDESAT(对于 ISO5x5x 和 UCC21750/59 为 9V)。

图 1:正常运行期间的 DESAT 系统

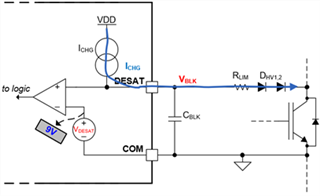

在过流/短路事件中(如图 2 所示),集电极/漏极电压将上升,HV 阻断二极管将反向偏置。充电电流现在为消隐电容器充电,在经过一段时间 tBLK 后超过内部阈值 VDESAT。在短暂的抗尖峰时间后,检测到一个 DESAT 事件,驱动器将关闭开关以防止损坏。

图 2:短路期间的 DESAT 系统

在此标准配置中,我们可以根据所选的 CBLK 以及固定参数 ICHG 和 VDESAT,非常简单地估算 tBLK,如 (1) 所示。

我们可以看到,从故障到关断的时间取决于充电电流 ICHG 和消隐电容器 CBLK 的值。如果我们需要更快的检测时间,则可以在一定程度上减小 CBLK(大约 100pF),但 CBLK 过小可能会提高误报率并降低抗噪性能,因为该电容器兼用作滤波器,通过 HV 二极管提供瞬变保护。在不提高充电电流的情况下,我们可以获得合理的 CBLK,并且仍然实现较短的 tBLK。内部电流源是固定的,因此我们必须使用外部元件来增大电流。

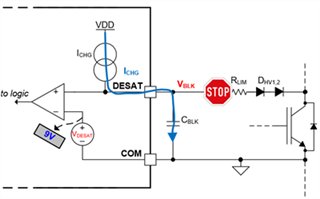

提高充电电流的最简单方法是添加电阻器,如图 3 所示。电阻器的头部可置于 OUT/OUT 或 VDD/VCC2 引脚上。置于 OUTH 上的好处是,额外的电流只会在开启期间流动,这是 DESAT 检测功能激活的唯一时间,从而节省一点功耗。

如果将电阻器置于 OUTH 上,则在关闭期间,如果使用负偏置电源,DESAT 可能会变为负值,但由于 RCHG 的作用,这不是问题,而且肖特基和齐纳二极管通常位于 DESAT 引脚和 COM 之间。此外,还可以使用肖特基二极管 DCHG 来防止关闭期间的电流反向流动。如果使用该二极管,则应将以下公式中的 VDD 替换为 (VDD−VF) 以补偿二极管的正向压降,但实际上,进行这种补偿不会显著改变计算。

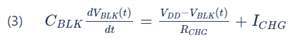

由于 RCHG 提供的电流取决于 VBLK 的值、DESAT 引脚上的值,其电流不是恒定的,而且计算

图 3:具有辅助电阻器配置的 DESAT

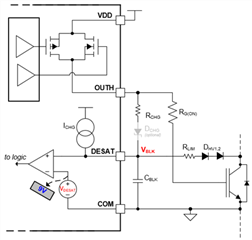

我们还可以在外部实现一个恒流源,例如图 4 中所示的基于 PNP 的电路,但这会增加成本、复杂性和 PCB 面积。使用恒流源时,tBLK 的估算也很简单,因为我们只需要对 ICHG 和 ICHG2 求和即可,如 (2) 所示。

图 4:具有外部恒流源的 DESAT

为了避免过于冗长的“推导”,可立即跳至结果。

根据基本的电容器电流关系,我们可以使用内部电流源以及 RCHG 上的电流(随时间变化)建立一个简单的微分方程,如 (3) 所示。

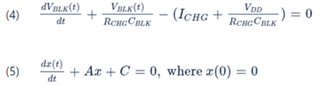

重新整理并除以 CBLK 可得到 (4),这是非常典型的 ODE 方程,如 (5) 所示,可直接求解。

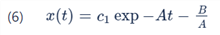

(5) 的广义解是 (6)。因此,我们可以轻松地替换我们的已知项并找到完整的表达式,其中 c1 基于我们的初始条件。

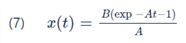

初始条件实际上取决于短路事件的类型。如果 IGBT/FET 开启后进入 短路状态(也称为硬开关故障或 HSF),则初始条件 VBLK(0) 将接近 0V。如果在正常 IGBT 导通期间发生过流/过载事件(称为负载故障或 FUL),则 CBLK 上将已经存在一定的电压,因为 ICHG 会在 HV 二极管和 RLIM 上产生电压。理想情况下,发生 HSF 事件时的消隐时间将比发生 FUL 事件时的消隐时间长,因此,我们选择考虑初始条件 VBLK(0)=0V。在此初始条件下,(6) 将变为 (7)。

对于不太喜欢用笔纸计算的人,我们也可以只使用 Matlab/Octave 通过下面的脚本找到解,然后可以轻松修改该脚本,从而根据所选的电路参数和固定参数(如 DESAT 阈值)进行计算求值。

Matlab Solution

|

clear; clc; syms vblk(t) t rchg cblk vdd vdesat ichg tblk; ic=vblk(0)==0; %set initial condition across blanking cap capcurr=cblk*diff(vblk,t)==(vdd-vblk)/rchg+ichg; %C*dv/dt = I(t), and we make a formula for pretty(capcurr); eq_blk = vdesat==dsolve(capcurr, ic); %Our voltage at desat pin is solved with the initial condition we set. blanktime=solve(eq_blk,t); pretty(tblk==blanktime); |

答案:我们现在根据内部电流源和辅助电阻器,可以找到 tBLK 的公式,如 (8) 所示