Other Parts Discussed in Thread: CSD18532KCS, LM5122

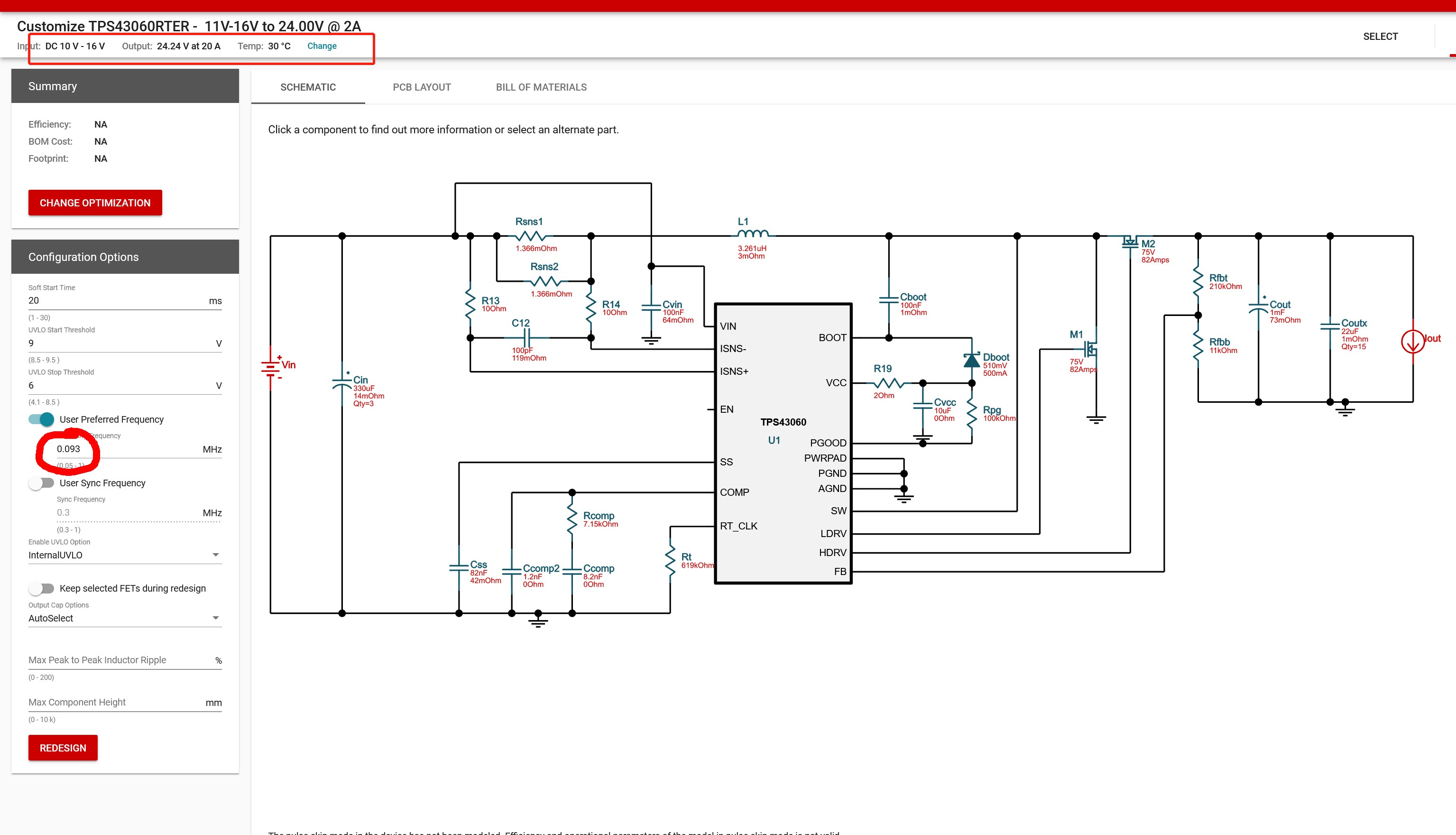

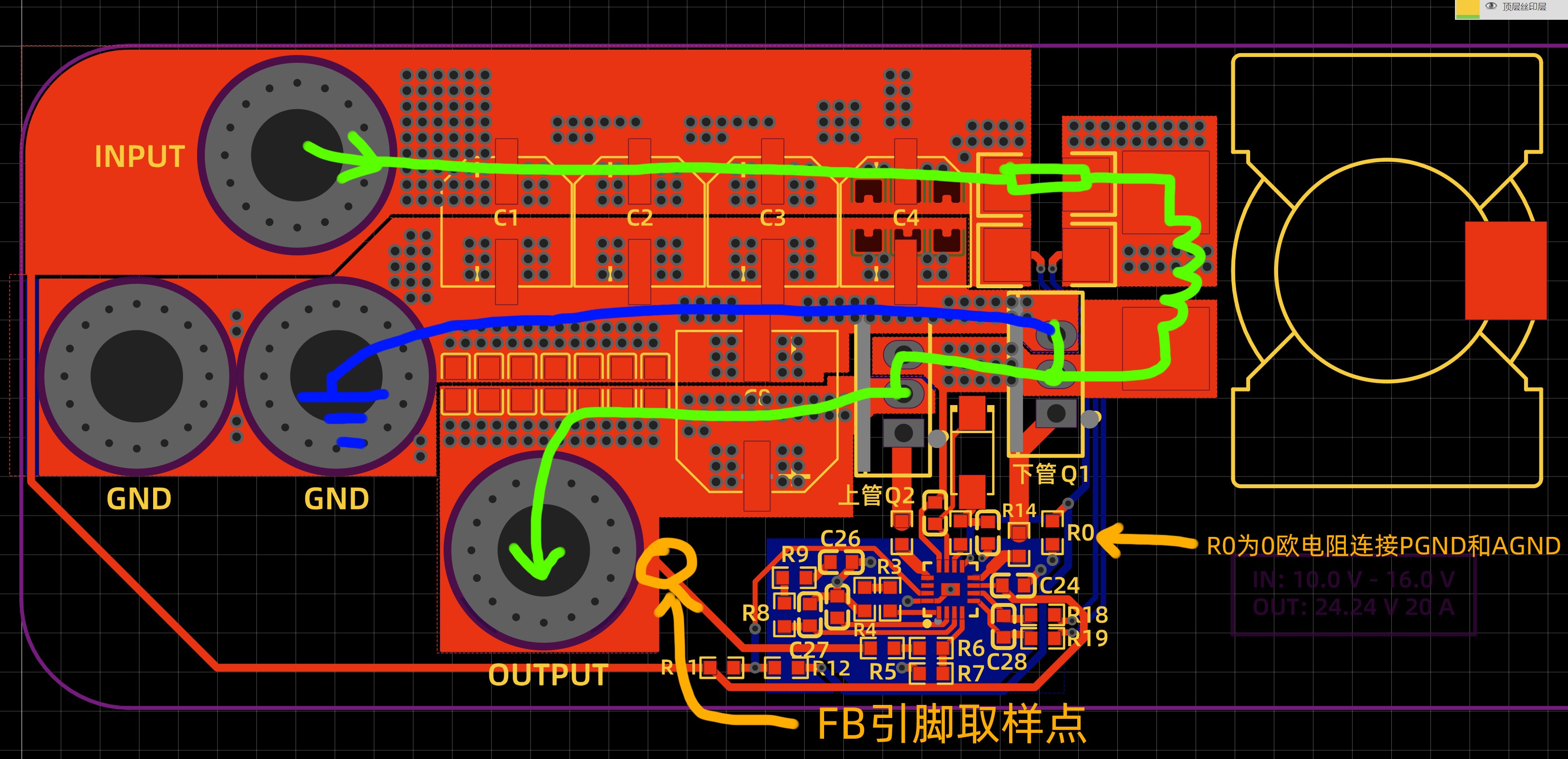

目前我使用 TPS43060 设计一款DC-DC产品。第一次做DC-DC不太熟练遇到了很多问题;

设计指标:

INPUT 12V

OUTPUT 24V,20A

开始,采样电阻【10毫欧】,很稳定。但是,输出电压随着负载的加大,而下降。这应该是限流起了作用。

电阻减小到【3毫欧】,输出电流大了很多,输出电压也稳定在24V。

由于我们需要更大的输出电流,我们继续减小电阻。

当我们将电阻将电阻减小到 【2毫欧】 或者 【1毫欧】 时,问题就出现了,效率大大下降,从之前的94%左右降低到了87%。MOS管发热变得明显。

按照手册上提供的公式,限制值随着电阻的减小而增大。但是,小到一定程度,似乎会带来麻烦。

不知道是不是太小的采样电阻,会让电路检测电流出现问题呢?

遇到这样的情况,该如何解决呢?