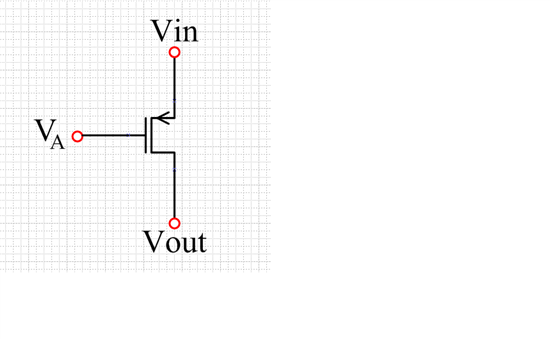

对于LDO,可简单理解为由一个调整管组成的电路(如图所示,假设调整管为PMOS),若输出电流为IO,当输入电压Vin比输出电压大很多时(调整管工作在饱和

区)的VGS0,先在扫描Vin,使得Vin逐渐减小,直到进入Dropout区;在Vin减小的过程中(忽略PMOS的VDS对ID的影响),当VDO=Vin-Vout较小使得管子进入线性区,由于线性区管子的输出电流会减小,而负载电流恒定为IO,监测环路为了保持输出电压Vout稳定,会调节PMOS的栅极电压VA,使得VGS增大,来维持输出电流IO的供应,此时管子仍然工作在线性区;且Vin继续减小时,会使得VGS迅速增大,当VGS增大到最大值(VA减小到其能达到的最小值,此时LDO进入Dropout区)后,Vin继续减小,VGS将相应减小,此后一段时间,LDO仍然工作在Dropout区。工作在Dropout区的LDO,其调整管可等效为一个电阻,且该等效电阻为该调整管所能达到的最小电阻。问题是,工作在Dropout区的调整管必定工作在线性区?线性区的电阻RDS=1/(Up*Cox*(VGS-VTH)*W/L),若工作在Dropout区的PMOS管,其输出电阻是线性区电阻表达式,则在进入Dropout区后,Vin的继续减小,其输出电阻会逐渐增大,但我在仿真中发现,Dropout区域还是比较大的,在Vin减小导致VGS减小过程中,IO基本不变,Dropout voltage也不变,从而RDS=Dropout/IO也不变,与线性区电阻表达相悖,请问,问题出在哪里?