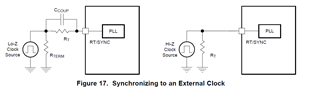

根据LMR14020-Q1的手册图17. synchronizing to an external clock

"When using a low impedance signal source, the frequency setting resistor RT is connected in parallel with an AC coupling capacitor CCOUP to a termination resistor RTERM (e.g., 50 Ω). The two resistors in series provide the default frequency setting resistance when the signal source is turned off."

1. 低阻抗时钟源为什么要按照左图连接?没有理解其中含义。

2. 如果FPGA输出时钟作为clock source, 是高阻抗还是低阻抗呢?

3. 我希望实现:有外部时钟源的时候开关频率和外部时钟源一致,没有时钟源时按照RT设置默认的频率。左图和右图均可实现吗?手册原文中,好像只有左图可以实现。