Other Parts Discussed in Thread: BQ24650

最近做的项目,由于有两个12V铅酸电池,想使用两个库仑计。与安卓系统I2C通讯。问题如下

1.这个方案是否可行

2.两个电池各接一个库仑计,能否共用一个采样电阻

3.由于安卓只引出一个I2C接口,请问两个库仑计是否可以接在一个I2C接口上

4.是否可以更改其中一个库仑计的地址从而区分电池bat1或者bat2

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

1,电池是一个主电池,一个备用电池,一个BQ24650太阳能充电芯片充电路径有自动切换,放电路径也是通过自动切换

2.能否使用两路USB转I2C或者USB转UART 再转HDQ

如下Technical Reference Manual手册中

9.6 Using UART Interface to HDQ

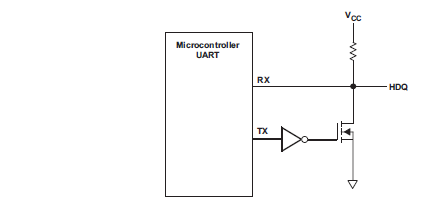

An implementation option for HDQ is to use a UART. An advantage to using the UART is that if the

UART is handling the communication and storing the results in a buffer, host processor interrupts during the

communication do not affect the timing of the HDQ communication with the HDQ target. Use of the UART for

HDQ communication requires that each word sent to or received from the UART is only a single bit of the

HDQ data or address. The procedure is to set the UART baud rate to 57,600 with no parity and two stop bits.

This yields a data word with 11 bits total (start bit, eight data bits, and two stop bits). At a baud rate of 57,600

(17.3 μs per bit), this is a total communication time of 190.9 μs and meets the required HDQ bit timing of 190

μs minimum. If data of 0xFE is sent to the UART, the transmitted data is low for 34.6 μs and then high for

the remaining bit time and is interpreted by the HDQ target as a 1. If data of 0xC0 is sent to the UART, the

transmitted data is low for 121.5 μs and then high for the remaining bit time and is interpreted by the HDQ target

as a 0. When data is sent to the host from the HDQ target, the received data could be interpreted as either

0xFE or 0xFC if a logic 1 is sent, or either 0xF0, 0xE0, 0xC0, 0x80, or 0x00 if a logic 0 is sent. A simple test

of the received data determines the received data bit. If the received data is greater than 0xF8, the data bit

should be interpreted as a logic 1, and if less than or equal to 0xF8, the data bit should be interpreted as a

logic 0. This analysis assumes the UART samples the received data approximately half-way through each of the

17.3-μs UART bit times, and that capacitive loading on the HDQ line may delay the rise time of the data a few

microseconds.

Note that the TX and RX of the UART must be tied together because HDQ is a single-wire interface. In case the

TX output is not an open-drain output, it needs to be converted to an open-drain output, as shown in Figure 9-5.

使用区分