您好,

為何BQ76952 REG1V8 引腳上的電壓在與MCU通訊後會被拉到3.3V

線路架構在 CFETOFF, DFETOFF, 有一外部上拉電阻到3.3V

Settings:Configuration:CFETOFF Pin Config 設置為 AA

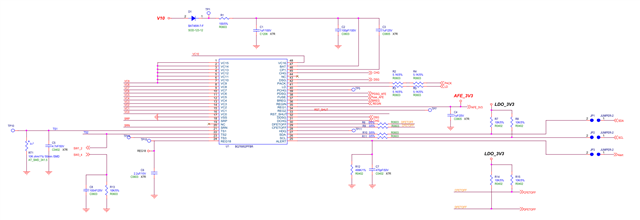

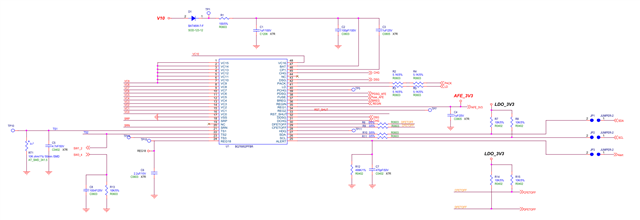

电路如貼圖

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

為何BQ76952 REG1V8 引腳上的電壓在與MCU通訊後會被拉到3.3V

線路架構在 CFETOFF, DFETOFF, 有一外部上拉電阻到3.3V

Settings:Configuration:CFETOFF Pin Config 設置為 AA

电路如貼圖

您好,

REG18 指示外接一顆2.2uF電容, 沒有接到其他地方,

GG文件 設定如下 :

| * Field Order: Class name | Subclass name | Parameter name | Parameter Value | Display Units |

| Settings | Fuse | Min Blow Fuse Voltage | 20000 | mV |

| Settings | Fuse | Fuse Blow Timeout | 30 | s |

| Settings | Configuration | Power Config | 2c81 | Hex |

| Settings | Configuration | REG12 Config | ed | Hex |

| Settings | Configuration | REG0 Config | 1 | Hex |

| Settings | Configuration | HWD Regulator Options | 1 | Hex |

| Settings | Configuration | Comm Type | 0 | — |

| Settings | Configuration | I2C Address | 0 | — |

| Settings | Configuration | SPI Configuration | 60 | — |

| Settings | Configuration | Comm Idle Time | 0 | s |

| Settings | Configuration | CFETOFF Pin Config | aa | Hex |

| Settings | Configuration | DFETOFF Pin Config | aa | Hex |

| Settings | Configuration | ALERT Pin Config | aa | Hex |

| Settings | Configuration | TS1 Config | 7 | Hex |

| Settings | Configuration | TS2 Config | b3 | Hex |

| Settings | Configuration | TS3 Config | 0 | Hex |

| Settings | Configuration | HDQ Pin Config | 0 | Hex |

| Settings | Configuration | DCHG Pin Config | 0c | Hex |

| Settings | Configuration | DDSG Pin Config | 0f | Hex |

| Settings | Configuration | DA Configuration | 5 | Hex |

| Settings | Configuration | Vcell Mode | 81ff | Hex |

| Settings | Configuration | CC3 Samples | 80 | Num |

| Settings | Protection | Protection Configuration | 2 | Hex |

| Settings | Protection | Enabled Protections A | fc | Hex |

| Settings | Protection | Enabled Protections B | f7 | Hex |

| Settings | Protection | Enabled Protections C | f0 | Hex |

| Settings | Protection | CHG FET Protections A | 98 | Hex |

| Settings | Protection | CHG FET Protections B | d5 | Hex |

| Settings | Protection | CHG FET Protections C | 56 | Hex |

| Settings | Protection | DSG FET Protections A | e4 | Hex |

| Settings | Protection | DSG FET Protections B | e6 | Hex |

| Settings | Protection | DSG FET Protections C | e2 | Hex |

| Settings | Protection | Body Diode Threshold | 50 | mA |

| Settings | Alarm | Default Alarm Mask | f801 | Hex |

| Settings | Alarm | SF Alert Mask A | fc | Hex |

| Settings | Alarm | SF Alert Mask B | f7 | Hex |

| Settings | Alarm | SF Alert Mask C | f4 | Hex |

| Settings | Alarm | PF Alert Mask A | 5f | Hex |

| Settings | Alarm | PF Alert Mask B | 9f | Hex |

| Settings | Alarm | PF Alert Mask C | 0 | Hex |

| Settings | Alarm | PF Alert Mask D | 0 | Hex |

| Settings | Permanent Failure | Enabled PF A | 0 | Hex |

| Settings | Permanent Failure | Enabled PF B | 0 | Hex |

| Settings | Permanent Failure | Enabled PF C | 0 | Hex |

| Settings | Permanent Failure | Enabled PF D | 0 | Hex |

| Settings | FET | FET Options | 3f | Hex |

| Settings | FET | Chg Pump Control | 5 | Hex |

| Settings | FET | Precharge Start Voltage | 0 | mV |

| Settings | FET | Precharge Stop Voltage | 0 | mV |

| Settings | FET | Predischarge Timeout | 50 | 10ms |

| Settings | FET | Predischarge Stop Delta | 100 | mV |

| Settings | Current Thresholds | Dsg Current Threshold | 100 | userA |

| Settings | Current Thresholds | Chg Current Threshold | 50 | userA |

| Settings | Cell Open-Wire | Check Time | 5 | s |

| Settings | Interconnect Resistances | Cell 1 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 2 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 3 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 4 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 5 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 6 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 7 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 8 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 9 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 10 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 11 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 12 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 13 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 14 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 15 Interconnect | 2 | mΩ |

| Settings | Interconnect Resistances | Cell 16 Interconnect | 2 | mΩ |

| Settings | Manufacturing | Mfg Status Init | 10 | Hex |

| Settings | Cell Balancing Config | Balancing Configuration | 9 | Hex |

| Settings | Cell Balancing Config | Min Cell Temp | 0 | °C |

| Settings | Cell Balancing Config | Max Cell Temp | 50 | °C |

| Settings | Cell Balancing Config | Max Internal Temp | 70 | °C |

| Settings | Cell Balancing Config | Cell Balance Interval | 20 | s |

| Settings | Cell Balancing Config | Cell Balance Max Cells | 3 | Num |

| Settings | Cell Balancing Config | Cell Balance Min Cell V (Charge) | 3800 | mV |

| Settings | Cell Balancing Config | Cell Balance Min Delta (Charge) | 100 | mV |

| Settings | Cell Balancing Config | Cell Balance Stop Delta (Charge) | 30 | mV |

| Settings | Cell Balancing Config | Cell Balance Min Cell V (Relax) | 3800 | mV |

| Settings | Cell Balancing Config | Cell Balance Min Delta (Relax) | 100 | mV |

| Settings | Cell Balancing Config | Cell Balance Stop Delta (Relax) | 30 | mV |

您好,请参考下面内容:

I've tested these settings and found that you are using SPI comm mode here but the CFETOFF pin is configured as Bits1:0 [ 1 0 = CFETOFF mode] . For the CFETOFF pin to be properly configured for SPI mode you need to set Bits1:0 to [ 0 0 = SPI_CS ] in the CFETOFF pin config. This should then have REG18 outputting 1.8V normally (writing 0xA8 to CFETOFF Pin Config register should do the trick).

您好,请参考下面内容

SPI Configuration register was set to 0x60 and thought this was being used in SPI mode.

We did manage to recreate what you are seeing and we recommend that you disable OPT1 (bit 3) in the DFETOFF/CFETOFF Pin config as this should fix the issue.