Other Parts Discussed in Thread: TPS3823

Hi, Johnsin.

上一個問題我已經先close了。

最後還是想要確定一個問題,我剛剛看了一下datasheet所提供的時序圖,裏面只有電源上電時觸發reset及wdi触發reset的時序,並沒有MR的部份。

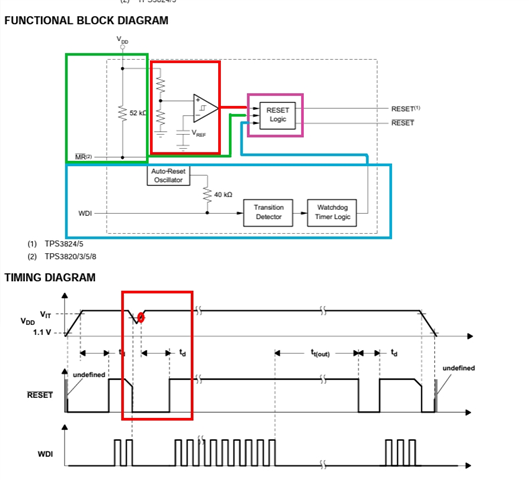

不過我看了一下BLOCK DIAGRAM,其實這顆RESET IC有這三種觸發,都會送一個訊號給RESET LOGIC BLOCK。

如果從電壓觸發的電路是一個比較器電路,由時序來看,當電壓掉下來時,也就是OP輸出為LOW,觸發RESET LOGIC中的RESET電路,此時RESET 輸出。

但是由時序圖來看,我有畫小紅圈的部份,電壓其實很快的又上升到正常的位置,也就是OP輸出為HIGH。

這輸入到RESET LOGIC的訊號,其實LOW到HIGH也是很短的時間。

可是RESET 輸出是完成了,一個固定的 T? + Td 時間。

是不是代表,當這個RESET LOGIC電路執行RESET 輸出動作時,此時RESET LOGIC BLOCK就不會受到外部的影響。不管輸入再如何變化,一定會固定完成一個RESET 時序。

目前看電壓變化造成的RESET 時序,是這樣。

我之前有接過一個電路,

WDI 不使用,設定為高阻抗。

MCU設定一個輸出,來控制RESET IC的MR腳。

RESET IC的 RESET 輸出再接回到 MCU 的RESET 輸入。

但這樣好像會RESET 不穩定。

當需要RESET 時

MCU讓TPS3823的MR為LOW

TPS3823 的RESET 輸出為LOW,讓MCU做RESET動作。

此時MCU的IO狀態為不確定狀態,直到MCU重新載入firmware。

MCU 讓MR腳位回覆到 HIGH。

目前我在想,是不是我應該要在MCU_GPO和TPS3823 的MR之間,加上一顆MOSFET,GATE一樣接到RESET 輸出。

當RESET 啟動時,就將GPO和MR切開來,因為 TPS3823 的MR有PULL HGIH,所以此時MR為HIGH。

也就是從RESET開始為LOW時(RESET動作一開始),MR就被拉為HIGH。這樣是否ok。

我目前電路是用這顆RESET IC,不過電路有點複雜,想說是否可以簡化。