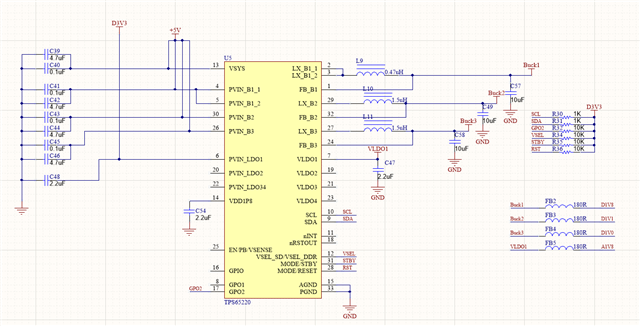

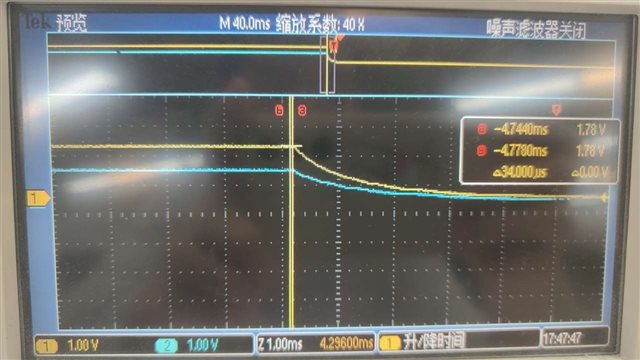

Hello, when I used the power management chip of TPS65220, I encountered the problem of incorrect power timing, which was not powered off in the order I set, but several channels were powered off at the same time. I checked for a week but did not find the problem, which may be due to my register configuration error or circuit diagram drawing error, please help me check the problem, thank you for your help.In the schematic above, I removed the R32 and R34 resistors and pulled VESL down to GND and pin 25 up to VSYS.

MPU6050_WriteReg(I2C_OFF, 0x01);

MPU6050_WriteReg(I2C_COMMUNICATION, 0x09);

MPU6050_WriteReg(ENABLE_CTRL, 0x0F);

MPU6050_WriteReg(LDO1_VOUT, 0x18);

MPU6050_WriteReg(BUCK3_VOUT, 0x10);

MPU6050_WriteReg(BUCK2_VOUT, 0x14);

MPU6050_WriteReg(BUCK1_VOUT, 0x24);

MPU6050_WriteReg(LDO1_SEQUENCE_SLOT, 0x43);

MPU6050_WriteReg(BUCK3_SEQUENCE_SLOT, 0x02);

MPU6050_WriteReg(BUCK2_SEQUENCE_SLOT, 0x43);

MPU6050_WriteReg(BUCK1_SEQUENCE_SLOT, 0x20); // 2 0

MPU6050_WriteReg(POWER_UP_SLOT_DURATION_1, 0x49);

MPU6050_WriteReg(POWER_UP_SLOT_DURATION_2, 0x40);

Delay_ms(300);

MPU6050_WriteReg(POWER_DOWN_SLOT_DURATION_1, 0x45);//0100_0101

// MPU6050_WriteReg(POWER_DOWN_SLOT_DURATION_2,0x00);

Delay_ms(300);

MPU6050_WriteReg(MFP_1_CONFIG, 0x40);//VSEL

Delay_ms(100);

MPU6050_WriteReg(MFP_2_CONFIG, 0x10); //0x80?可配置为PB模式 0x10

Delay_ms(100);

MPU6050_WriteReg(STBY_EN, 0x0F);

Delay_ms(100);

MPU6050_WriteReg(GENERAL_CONFIG, 0x08);

Delay_ms(100);

MPU6050_WriteReg(UV_MASK, 0x7F);//有无必要

Delay_ms(100);

MPU6050_WriteReg(NVM_PROGARMMING, 0x0A);

Delay_ms(100);

MPU6050_WriteReg(NVM_VALIDATION, 0x07);