This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

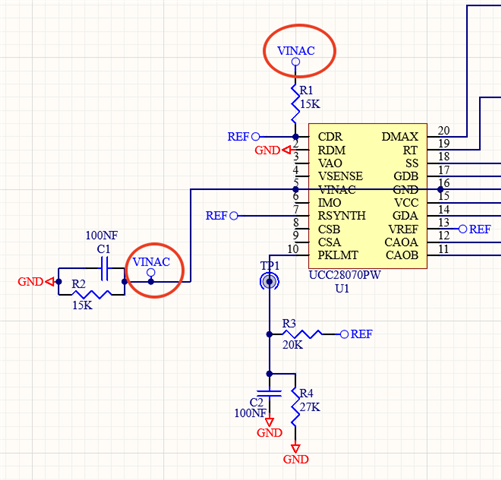

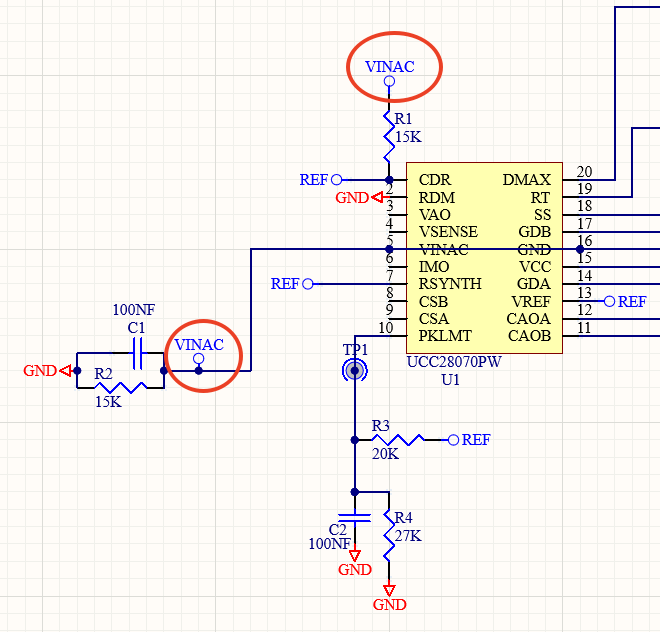

TA = –40°C to 125°C, TJ = TA, VCC = 12 V, GND = 0 V, RRT = 75 kΩ, RDMX = 68.1 kΩ, RRDM = RSYN = 100 kΩ, CCDR = 2.2 nF, CSS = CVREF = 0.1 μF, CVCC = 1 μF, IVREF = 0 mA (unless otherwise noted)

如图表是在以上的测试条件下给出的相关测试等到的数据,且2.6V是TYP实际应用中同样的条件下,值应该在2.6V左右。

您好

根据datasheet说明 Kvff在如表情况下是相对固定的。详细说明如下:

A great benefit of the QVFF architecture is that the fixed kVFF factors eliminate any contribution to distortion of the multiplier output, unlike an externally-filtered VINAC signal which unavoidably contains 2nd-harmonic distortion components. Furthermore, the QVFF algorithm allows for rapid response to both increasing and decreasing changes in input rms voltage so that disturbances transmitted to the PFC output are minimized. 5% hysteresis in the level thresholds help avoid chattering between QVFF levels for VVINAC voltage peaks near a particular threshold or containing mild ringing or distortion. The QVFF architecture requires that the input voltage be largely sinusoidal, and relies on detecting zero-crossings to adjust QVFF downward on decreasing input voltage. Zerocrossings are defined as VVINAC falling below 0.7 V for at least 50 μs, typically.