Part Number: UCC21520

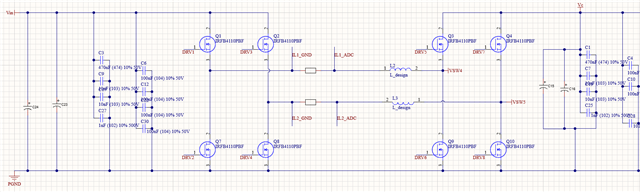

你好,我目前在做一个两相交错并联四开关的功率板,

这是电路拓扑

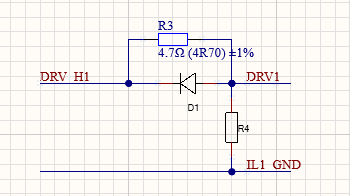

这是驱动电阻和栅极电阻(10K)

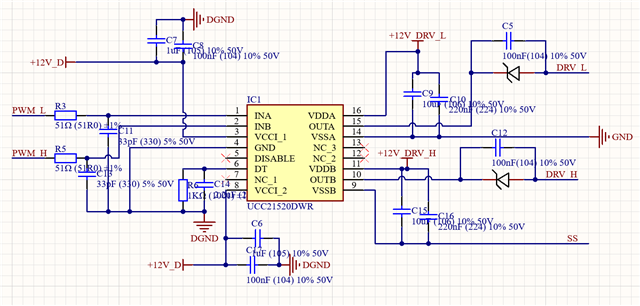

这是UCC21520的驱动电路

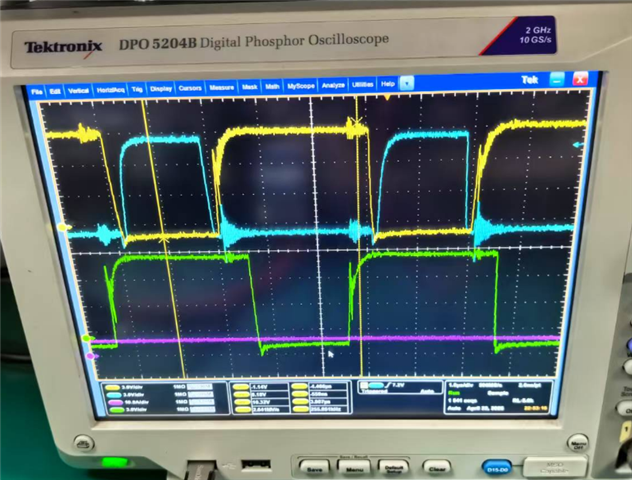

目前在加入几百W功率之后出现了如下问题:

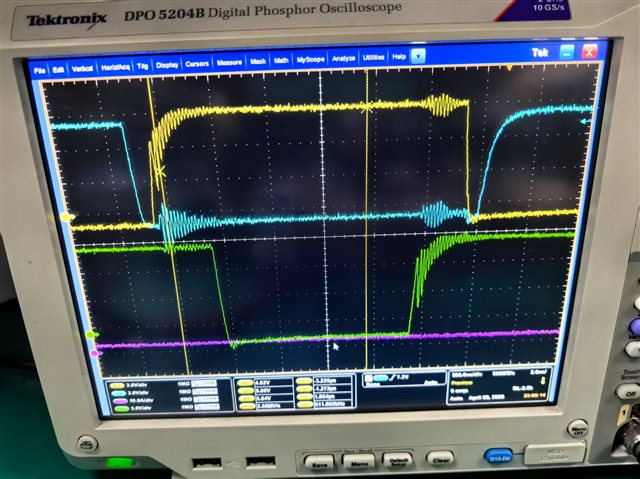

电路工作在buck模式,所测波形为直接测MOS管引脚GS,其中黄色为第一张主电路原理图中桥臂上管Q1,蓝色为桥臂下管Q7,绿色为第二相桥臂上管Q2

在两个上桥臂都同时导通的时候,驱动GS会出现振荡,同时可能是由于串扰问题引起其他mos管驱动gs振荡,之前考虑的是寄生电感的原因,但是振铃一般不是在驱动电压幅值上下衰减振荡的吗?而且下管的开通(图蓝色波形)好像没有这个影响?请问这是大概是什么原因呢?我的驱动电路设计的对吗

这个是Uds波形,会出现振铃 串扰问题