Hi Daniel

多谢回复,我查阅了你提供的这一份规格书,如果按默认配置,应该是only usb3.1 mode的配置;

我们现在的设计为通过i2c进行控制,需求是后端Type-C接口可能接DP屏,也可能接usb3.1的外设,所以默认的寄存器配置应该无法满足要求,针对我们的需求场景,不考虑EQ等配置的情况下,如下的reg配置是否满足,请帮忙double check下:

0x0a - 0x03 //2lane dp 2lane usb,FLIPSEL bit待获取到正反插信息后进行控制

0x10 - 0x00 //default value

0x11 - 0x00 //default value

0x12 - 0x00//read only, no need config

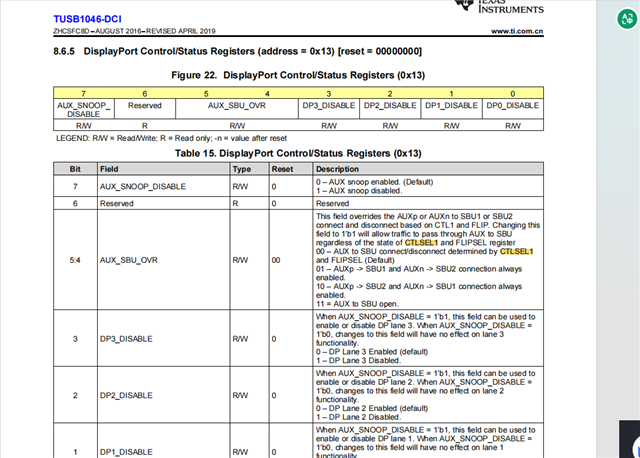

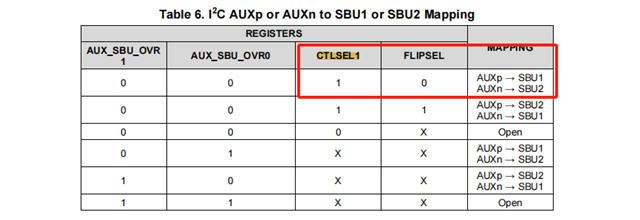

0x13 - 0x00//此时默认配置AUX以正插状态连接通路,因为0x0a配置的0x03

0x20 - 0x00//default value

0x21 - 0x00//read only, no need config

0x22 - 0x04//default value

问题:

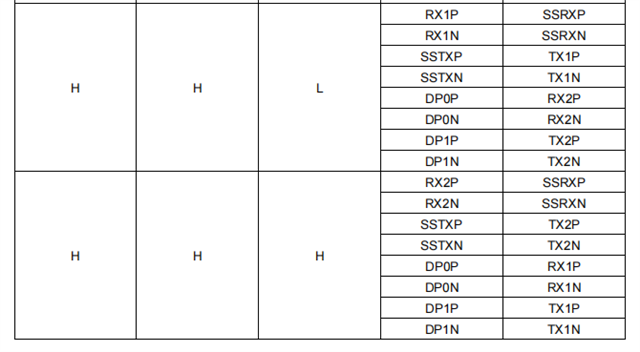

1.关于高速差分信号的通路配置,是否可以参考Table 4,比如当前配置的是0x0a - 0x03,FLIPSEL bit的0/1是否就对应Table 4中的FLIP pin高低状态?

2.0x13配置默认值0x00,表示4lane DP都enable,此时是否会影响usb通路?

3.按照上述分析,是否只需要根据插入方向更新FLIPSEL bit位即可?