Part Number: DRA829J

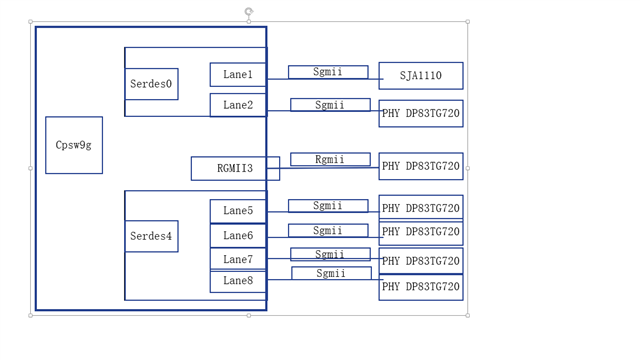

1. we are using the TI DP83TG720 Ethernet PHY using the SGMII interface between the SOC and PHY

2. apply TDA4VM: SGMII interface not communicating with PHY(DP83TG720) in SDK9.2 for J721E - Processors forum - Processors - TI E2E support forums, eth1-eth6 can link up ; but only lane2 sgmii can link, lane5 - lane8 sgmii can not link ;

3. some content in k3-j721e-common-proc-board.dts

&serdes_ln_ctrl {

idle-states = //<J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_PCIE0_LANE1>,

<J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_QSGMII_LANE2>,

<J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_PCIE2_LANE0>, <J721E_SERDES2_LANE1_PCIE2_LANE1>,

<J721E_SERDES3_LANE0_USB3_0_SWAP>, <J721E_SERDES3_LANE1_USB3_0>,

//<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

<J721E_SERDES4_LANE0_QSGMII_LANE5>, <J721E_SERDES4_LANE1_QSGMII_LANE6>,

//<J721E_SERDES4_LANE2_EDP_LANE2>, <J721E_SERDES4_LANE3_EDP_LANE3>;

<J721E_SERDES4_LANE2_QSGMII_LANE7>, <J721E_SERDES4_LANE3_QSGMII_LANE8>;

};

&serdes_wiz3 {

typec-dir-gpios = <&main_gpio1 3 GPIO_ACTIVE_HIGH>;

typec-dir-debounce-ms = <700>; /* TUSB321, tCCB_DEFAULT 133 ms

};

&serdes3 {

serdes3_usb_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_USB3>;

resets = <&serdes_wiz3 1>, <&serdes_wiz3 2>;

};

};

&cpsw0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&main_mdio0_pins_default &main_rgmii2_pins_def

};

&cpsw9g_mdio {

status = "okay";

#address-cells = <1>;

#size-cells = <0>;

cpsw9g_phy0: ethernet-phy@4 {

reg = <4>;

};

cpsw9g_phy3: ethernet-phy@13 {

reg = <13>;

};

cpsw9g_phy5: ethernet-phy@5 {

reg = <5>;

};

cpsw9g_phy6: ethernet-phy@8 {

reg = <8>;

};

cpsw9g_phy7: ethernet-phy@10 {

reg = <10>;

};

cpsw9g_phy8: ethernet-phy@12 {

reg = <12>;

};

};

&cpsw0_port1 {

status = "disabled";

};

&cpsw0_port2 {

status = "okay";

phy-handle = <&cpsw9g_phy0>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 2>, <&serdes0_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port3 {

status = "okay";

phy-handle = <&cpsw9g_phy3>;

phy-mode = "rgmii-id";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 3>;

}; //rgmii

&cpsw0_port4 {

status = "disabled";

};

&cpsw0_port5 {

status = "okay";

phy-handle = <&cpsw9g_phy5>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 5>, <&serdes4_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port6 {

status = "okay";

phy-handle = <&cpsw9g_phy6>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 6>, <&serdes4_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port7 {

status = "okay";

phy-handle = <&cpsw9g_phy7>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 7>, <&serdes4_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&cpsw0_port8 {

status = "okay";

phy-handle = <&cpsw9g_phy8>;

phy-mode = "sgmii";

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 8>, <&serdes4_sgmii_link>;

phy-names = "portmode", "serdes-phy";

};

&mcu_cpsw {

pinctrl-names = "default";

pinctrl-0 = <&mcu_cpsw_pins_default &mcu_mdio_pins_default>;

cpts@3d000 {

/* Map HW4_TS_PUSH to GENF1 */

ti,pps = <3 1>;

};

};

&davinci_mdio {

phy0: ethernet-phy@0 {

reg = <0>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

&cpsw_port1 {

phy-mode = "rgmii-rxid";

phy-handle = <&phy0>;

};

&dss {

/*

* These clock assignments are chosen to enable the following outputs:

*

* VP0 - DisplayPort SST

* VP1 - DPI0

* VP2 - DSI

* VP3 - DPI1

*/

assigned-clocks = <&k3_clks 152 1>,

<&k3_clks 152 4>,

<&k3_clks 152 9>,

<&k3_clks 152 13>;

assigned-clock-parents = <&k3_clks 152 2>, /* PLL16_HSDIV0 */

<&k3_clks 152 6>, /* PLL19_HSDIV0 */

<&k3_clks 152 11>, /* PLL18_HSDIV0 */

<&k3_clks 152 18>; /* PLL23_HSDIV0 */

};

&dss_ports {

port {

dpi0_out: endpoint {

remote-endpoint = <&dp0_in>;

};

};

};

&dp0_ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dp0_in: endpoint {

remote-endpoint = <&dpi0_out>;

};

};

port@4 {

reg = <4>;

dp0_out: endpoint {

remote-endpoint = <&dp_connector_in>;

};

};

};

&mcasp10 {

status = "okay";

#sound-dai-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&mcasp10_pins_default>;

op-mode = <0>; /* MCASP_IIS_MODE */

tdm-slots = <2>;

auxclk-fs-ratio = <256>;

serial-dir = < /* 0: INACTIVE, 1: TX, 2: RX */

1 1 1 1

2 2 2 0

>;

tx-num-evt = <0>;

rx-num-evt = <0>;

};

&cmn_refclk1 {

clock-frequency = <100000000>;

};

/*

&wiz0_pll1_refclk {

assigned-clocks = <&wiz0_pll1_refclk>;

assigned-clock-parents = <&cmn_refclk1>;

};

*/

&wiz0_refclk_dig {

assigned-clocks = <&wiz0_refclk_dig>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz1_pll1_refclk {

assigned-clocks = <&wiz1_pll1_refclk>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz1_refclk_dig {

assigned-clocks = <&wiz1_refclk_dig>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz2_pll1_refclk {

assigned-clocks = <&wiz2_pll1_refclk>;

assigned-clock-parents = <&cmn_refclk1>;

};

&wiz2_refclk_dig {

assigned-clocks = <&wiz2_refclk_dig>;

assigned-clock-parents = <&cmn_refclk1>;

};

&serdes_wiz0 {

status = "okay";

};

&serdes_wiz1 {

status = "disabled";

};

&serdes_wiz2 {

status = "disabled";

};

&serdes_wiz4 {

status = "okay";

};

&serdes0 {

status = "okay";

assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>,<&serdes0 CDNS_SIERRA_PLL_CMNLC1>;

assigned-clock-parents = <&wiz0_pll1_refclk>,<&wiz0_pll1_refclk>;

serdes0_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz0 1>;

};

serdes0_sgmii_link: phy@1 {

reg = <1>;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz0 2>;

};

};

&serdes1 {

assigned-clocks = <&serdes1 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz1_pll1_refclk>;

status = "disabled";

serdes1_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>;

};

};

&serdes2 {

status = "disabled";

assigned-clocks = <&serdes2 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz2_pll1_refclk>;

serdes2_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz2 1>, <&serdes_wiz2 2>;

};

};

&serdes4 {

status = "okay";

assigned-clocks = <&serdes4 CDNS_SIERRA_PLL_CMNLC>;

assigned-clock-parents = <&wiz4_pll0_refclk>;

serdes4_sgmii_link: phy@0 {

reg = <0>;

cdns,num-lanes = <4>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz4 1>, <&serdes_wiz4 2>, <&serdes_wiz4 3>, <&serdes_wiz4 4>;

};

};

4.some content in k3-j721e-main.dts

serdes_wiz4: wiz@5050000 {

//compatible = "ti,am64-wiz-10g";

compatible = "ti,j721e-wiz-10g";

#address-cells = <1>;

#size-cells = <1>;

power-domains = <&k3_pds 297 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 297 1>, <&k3_clks 297 9>, <&cmn_refc

clock-names = "fck", "core_ref_clk", "ext_ref_clk";

assigned-clocks = <&k3_clks 297 9>;

//assigned-clock-parents = <&k3_clks 297 10>;

assigned-clock-parents = <&k3_clks 297 13>;

assigned-clock-rates = <19200000>;

num-lanes = <4>;

#reset-cells = <1>;

//#clock-cells = <1>;

ranges = <0x05050000 0x00 0x05050000 0x010000>,

<0x0a030a00 0x00 0x0a030a00 0x40>;

wiz4_pll0_refclk: pll0-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll0_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll0_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_pll1_refclk: pll1-refclk {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_pll1_refclk";

#clock-cells = <0>;

assigned-clocks = <&wiz4_pll1_refclk>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_refclk_dig: refclk-dig {

clocks = <&k3_clks 297 9>, <&cmn_refclk>;

clock-output-names = "wiz4_refclk_dig";

#clock-cells = <0>;

assigned-clocks = <&wiz4_refclk_dig>;

assigned-clock-parents = <&k3_clks 297 9>;

};

wiz4_cmn_refclk_dig_div: cmn-refclk-dig-div {

clocks = <&wiz4_refclk_dig>;

#clock-cells = <0>;

};

wiz4_cmn_refclk1_dig_div: cmn-refclk1-dig-div {

clocks = <&wiz4_pll1_refclk>;

#clock-cells = <0>;

};

serdes4: serdes@5050000 {

/*

* Note: we also map DPTX PHY registers as the Torr

* needs to manage those.

*/

compatible = "ti,j721e-serdes-10g";

reg = <0x05050000 0x010000>,

<0x0a030a00 0x40>; /* DPTX PHY */

reg-names = "torrent_phy", "dptx_phy";

resets = <&serdes_wiz4 0>;

reset-names = "torrent_reset";

//clocks = <&serdes_wiz4 TI_WIZ_PLL0_REFCLK>;

clocks = <&wiz4_pll0_refclk>;

clock-names = "refclk";

/* assigned-clocks = <&serdes_wiz4 TI_WIZ_PLL0_REFCLK>

<&serdes_wiz4 TI_WIZ_PLL1_REFCLK>,

<&serdes_wiz4 TI_WIZ_REFCLK_DIG>;

assigned-clock-parents = <&k3_clks 297 9>,

<&k3_clks 297 9>,

<&k3_clks 297 9>;

*/

#address-cells = <1>;

#size-cells = <0>;

};

};

5. dmesg | grep eth

0.000000] OF: reserved mem: initialized node vision-apps-r5f-virtual-eth-queues@e4000000, compatible id shared-dma-pool

[ 0.000000] OF: reserved mem: initialized node vision-apps-r5f-virtual-eth-buffers@e4800000, compatible id shared-dma-pool

[ 0.000000] psci: probing for conduit method from DT.

[ 0.832840] optee: probing for conduit method.

[ 2.312482] am65-cpsw-nuss 46000000.ethernet: initializing am65 cpsw nuss version 0x6BA00101, cpsw version 0x6BA80100 Ports: 2 quirks:00000000

[ 2.325296] am65-cpsw-nuss 46000000.ethernet: initialized cpsw ale version 1.4

[ 2.332501] am65-cpsw-nuss 46000000.ethernet: ALE Table size 64

[ 2.342905] am65-cpsw-nuss 46000000.ethernet: CPTS ver 0x4e8a010a, freq:500000000, add_val:1 pps:1

[ 3.787172] am65-cpsw-nuss c000000.ethernet: initializing am65 cpsw nuss version 0x6BA01901, cpsw version 0x6BA80101 Ports: 9 quirks:00000000

[ 3.799961] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 3.806283] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 3.812595] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 3.818904] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 3.825211] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 3.831518] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 3.837777] am65-cpsw-nuss c000000.ethernet: initialized cpsw ale version 1.4

[ 3.844895] am65-cpsw-nuss c000000.ethernet: ALE Table size 512

[ 3.851235] am65-cpsw-nuss c000000.ethernet: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0

[ 4.064472] am65-cpsw-nuss 46000000.ethernet: initializing am65 cpsw nuss version 0x6BA00101, cpsw version 0x6BA80100 Ports: 2 quirks:00000000

[ 4.077300] am65-cpsw-nuss 46000000.ethernet: initialized cpsw ale version 1.4

[ 4.084512] am65-cpsw-nuss 46000000.ethernet: ALE Table size 64

[ 4.094873] am65-cpsw-nuss 46000000.ethernet: CPTS ver 0x4e8a010a, freq:500000000, add_val:1 pps:1

[ 4.105409] am65-cpsw-nuss 46000000.ethernet: set new flow-id-base 48

[ 5.551306] am65-cpsw-nuss c000000.ethernet: initializing am65 cpsw nuss version 0x6BA01901, cpsw version 0x6BA80101 Ports: 9 quirks:00000000

[ 5.564121] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 5.570440] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 5.576756] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 5.583063] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 5.589370] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 5.595687] am65-cpsw-nuss c000000.ethernet: Use random MAC address

[ 5.601944] am65-cpsw-nuss c000000.ethernet: initialized cpsw ale version 1.4

[ 5.609061] am65-cpsw-nuss c000000.ethernet: ALE Table size 512

[ 5.615373] am65-cpsw-nuss c000000.ethernet: CPTS ver 0x4e8a010a, freq:200000000, add_val:4 pps:0

[ 5.626254] am65-cpsw-nuss c000000.ethernet: set new flow-id-base 140

[ 7.020162] systemd[1]: /lib/systemd/system/bt-enable.service:9: Standard output type syslog is obsolete, automatically updating to journal. Please update your unit file, and consider removing the setting altogether.

[ 7.074647] systemd[1]: /etc/systemd/system/sync-clocks.service:11: Standard output type syslog is obsolete, automatically updating to journal. Please update your unit file, and consider removing the setting altogether.

[ 11.359630] am65-cpsw-nuss c000000.ethernet eth6: PHY [c000f00.mdio:0c] driver [TI DP83TG720CS1.1] (irq=POLL)

[ 11.369739] am65-cpsw-nuss c000000.ethernet eth6: configuring for phy/sgmii link mode

[ 11.895230] am65-cpsw-nuss c000000.ethernet eth5: PHY [c000f00.mdio:0a] driver [TI DP83TG720CS1.1] (irq=POLL)

[ 11.905253] am65-cpsw-nuss c000000.ethernet eth5: configuring for phy/sgmii link mode

[ 12.361748] am65-cpsw-nuss c000000.ethernet eth4: PHY [c000f00.mdio:08] driver [TI DP83TG720CS1.1] (irq=POLL)

[ 12.383482] am65-cpsw-nuss c000000.ethernet eth4: configuring for phy/sgmii link mode

[ 13.031459] am65-cpsw-nuss c000000.ethernet eth3: PHY [c000f00.mdio:05] driver [TI DP83TG720CS1.1] (irq=POLL)

[ 13.041533] am65-cpsw-nuss c000000.ethernet eth3: configuring for phy/sgmii link mode

[ 13.486003] am65-cpsw-nuss c000000.ethernet eth2: PHY [c000f00.mdio:0d] driver [TI DP83TG720CS1.1] (irq=POLL)

[ 13.496252] am65-cpsw-nuss c000000.ethernet eth2: configuring for phy/rgmii-id link mode

[ 13.903279] am65-cpsw-nuss c000000.ethernet eth1: PHY [c000f00.mdio:04] driver [TI DP83TG720CS1.1] (irq=POLL)

[ 13.913322] am65-cpsw-nuss c000000.ethernet eth1: configuring for phy/sgmii link mode

[ 13.969159] am65-cpsw-nuss 46000000.ethernet eth0: validation of rgmii-rxid with support 00000000,00000000,00006280 and advertisement 00000000,00000000,00002280 failed: -EINVAL

[ 18.536994] am65-cpsw-nuss c000000.ethernet eth4: Link is Up - 1Gbps/Full - flow control off

[ 18.545464] IPv6: ADDRCONF(NETDEV_CHANGE): eth4: link becomes ready

root@j721e-evm:~#

6 ethtool eth4 (lane 5)

Settings for eth4:

Supported ports: [ TP MII ]

Supported link modes: 1000baseT/Full

Supported pause frame use: Symmetric

Supports auto-negotiation: No

Supported FEC modes: Not reported

Advertised link modes: Not reported

Advertised pause frame use: Symmetric

Advertised auto-negotiation: No

Advertised FEC modes: Not reported

Speed: 1000Mb/s

Duplex: Full

Auto-negotiation: off

Port: Twisted Pair

PHYAD: 8

Transceiver: external

MDI-X: Unknown

Supports Wake-on: d

Wake-on: d

Current message level: 0x000020f7 (8439)

drv probe link ifdown ifup rx_err tx_err hw

Link detected: yes

7. only port2 sgmii can link

root@j721e-evm:~# devmem2 0x0c000214

/dev/mem opened.

Memory mapped at address 0xffff96515000.

Read at address 0x0C000214 (0xffff96515214): 0x0000003D

root@j721e-evm:~# devmem2 0x0c000514

/dev/mem opened.

Memory mapped at address 0xffffbc7ba000.

Read at address 0x0C000514 (0xffffbc7ba514): 0x00000000

root@j721e-evm:~# devmem2 0x0c000614

/dev/mem opened.

Memory mapped at address 0xffff886d8000.

Read at address 0x0C000614 (0xffff886d8614): 0x0000003C

root@j721e-evm:~# devmem2 0x0c000714

/dev/mem opened.

Memory mapped at address 0xffff962d7000.

Read at address 0x0C000714 (0xffff962d7714): 0x00000000

root@j721e-evm:~# devmem2 0x0c000814

/dev/mem opened.

Memory mapped at address 0xffffad207000.

Read at address 0x0C000814 (0xffffad207814): 0x00000000

root@j721e-evm:~# devmem2 0x0c000314

/dev/mem opened.

Memory mapped at address 0xffff920f0000.

Read at address 0x0C000314 (0xffff920f0314): 0x00000028

root@j721e-evm:~#

8. question:

Can you help me check the DTS content,and tell me what modifications should be do can make SGMII 5/6/7/8 work, thanks.