Part Number: TDA4VM

1、TDA4VM 的ISP流程包含VISS DCC LDC MSC DSS ;

2、目前通过edgeai-tidl-tools工具可以将自定义的模型处理RAW数据然后输出RAW数据。

问题:

需要实现从CSI2取出RAW数据,经过TIDL-C7xDSP/MMA处理后,再将模型处理后的RAW数据送回ISP处理,这个流程TDA4VM是否支持呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

1、TDA4VM 的ISP流程包含VISS DCC LDC MSC DSS ;

是的,这是可能的。CSIRX将数据输出到内存中,一旦进入内存,就可以发送给C7x进行处理,然后再进行处理输出,如果仍然是RAW数据,可以在ISP中进行进一步处理。

需要实现从CSI2取出RAW数据,经过TIDL-C7xDSP/MMA处理后,再将模型处理后的RAW数据送回ISP处理,这个流程TDA4VM是否支持呢?

是的,这是可能的。CSIRX将数据输出到内存中,一旦进入内存,就可以发送给C7x进行处理,然后再进行处理输出,如果仍然是RAW数据,可以在ISP中进行进一步处理。

您好:

CSI-RX将数据输出到内存中,取RAW数据经过TIDL-C7xDSP/MMA处理后输出RAW数据,最后将处理后的RAW数据回灌到ISP

1、这样的开发流程,一般基于LINUX-SDK进行快速验证开发么?

2、目前贵司是否存在这样的demo数据流处理呢,是否也是基于LINUX-SDK的Demo呢?

3、CSI-RX将RAW数据放到内存中,模型处理后的数据需要保持怎样的数据格式,才能被ISP(VISS)接收?

4、如何将处理后的RAW进行数据回灌,才能让ISP(VISS)接收内存中处理后的数据,而不是直接从CSIRX接收RAW数据呢?

1、这样的开发流程,一般基于LINUX-SDK进行快速验证开发么?

是的,在这种情况下可以使用带有OpenVX框架的Linux。

2、目前贵司是否存在这样的demo数据流处理呢,是否也是基于LINUX-SDK的Demo呢?

不完全是,但你可以参考多摄像头演示。顺便说一句,这是在内部论坛上发布的。

3、CSI-RX将RAW数据放到内存中,模型处理后的数据需要保持怎样的数据格式,才能被ISP(VISS)接收?

VISS支持许多2x2数据格式,如拜耳格式。它可以将此作为输入,并可以生成像YUV这样的可视格式。

4、如何将处理后的RAW进行数据回灌,才能让ISP(VISS)接收内存中处理后的数据,而不是直接从CSIRX接收RAW数据呢?

您需要在这里正确地连接不同的组件。

您好:

1、目前贵司是否存在这样的demo数据流处理呢,是否也是基于LINUX-SDK的Demo呢?

不完全是,但你可以参考多摄像头演示。顺便说一句,这是在内部论坛上发布的。

问题:

目前你提到多摄像头演示,说在内部论坛上发布,那就是目前LINUX和RTOS的SDK文档是没有这个资料,对么?

如果是在内部论坛上,有具体的链接么?

2、如何将处理后的RAW进行数据回灌,才能让ISP(VISS)接收内存中处理后的数据,而不是直接从CSIRX接收RAW数据呢?

您需要在这里正确地连接不同的组件。

问题a:

这里如何将处理后的RAW进行数据回灌到ISP(VISS)中呢?你所说需要正确的连接不同的组件,是否有实现这种数据链的demo呢?

正确连接不同的组件,需要那些组件进行正确顺序的连接?如何在代码中实现?

问题b:

我们TDA4VM的ISP(VISS)默认是online模式接收CSI2-RX数据,如何设置或者代码实现ISP(VISS)处于offline模式,进行接收回灌的RAW数据呢?

目前在DSP上还没有处理RAW图像数据的算法。

不,我的意思是多镜头演示是最近的演示,我们可以参考。这在RTOS SDK中已经得到了支持。它使用OpenVX框架将CSIRX连接到ISP。客户必须在CSIRX和ISP之间插入DSP处理。

没关系。CSIRX输出将存储在内存中,我认为DSP处理的输出也将存储在内存中。客户需要使用OpenVX框架编写DSP节点和内核,然后他们需要将该节点与输入端的CSIRX和输出端的ISP节点正确连接起来。

这里如何将处理后的RAW进行数据回灌到ISP(VISS)中呢?你所说需要正确的连接不同的组件,是否有实现这种数据链的demo呢?

正确连接不同的组件,需要那些组件进行正确顺序的连接?如何在代码中实现?

正如我提到的,我们在SDK中没有这样的演示。

问题b:

我们TDA4VM的ISP(VISS)默认是online模式接收CSI2-RX数据,如何设置或者代码实现ISP(VISS)处于offline模式,进行接收回灌的RAW数据呢?

不,ISP已经从内存中读取数据了。

您好 Links:

1、我们目前已经在PC端使用TDIL工具用自己的模型编译且推理出RAW的数据源

2、基于您的回答

我理解为CSI2-RX输出将直接存储在内存中,并且ISP(VPAC)也是直接从内存中读取数据;

目前需要做的工作就是使用OpenVX框架编写DSP节点和内核,然后获取CSI2-RX存储的内存,更新DSP处理后数据RAW填充到ISP(VPAC)读取的内存地址。

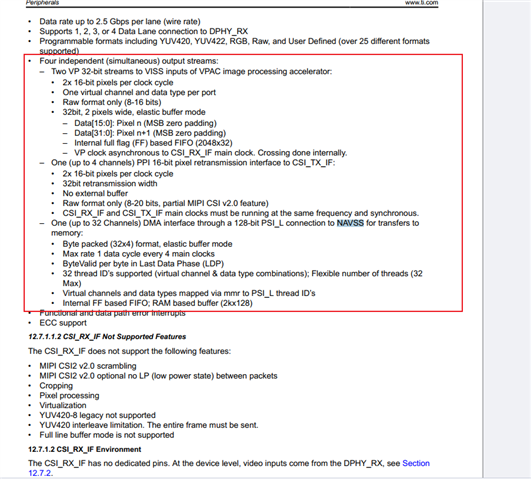

3、基于TRM技术手册的参考

这里CSI_RX_IF三个独立可同时输出流VPAC、CSI_TX_IF、DMA-NAVSS

问题:

1、CSI_RX_IF默认独立出流到DMA-NAVSS么?还是同时启用VPAC与DMA?如果默认是DMA,那以下两个问题如何查询确认?

2、CSI2-RX存储的内存地址,如何获取呢?

3、ISP(VPAC)读取数据内存地址,如何获取呢?

4、三个独立可同时输出流VPAC、CSI_TX_IF、DMA-NAVSS,是通过什么控制CSI_RX_IF往哪一个流进行输出呢?

非常感谢,致敬!!!

1、CSI_RX_IF默认独立出流到DMA-NAVSS么?还是同时启用VPAC与DMA?如果默认是DMA,那以下两个问题如何查询确认?

不需要,CSIRX可以独立输出到DDR,不需要使能VPAC DMA。事实上,在一致性测试中有独立的OpenVX示例,只是启用了CSIRX。

.

2、CSI2-RX存储的内存地址,如何获取呢?

实际上是另一种方式,我们需要分配缓冲区并向驱动程序提供缓冲区地址。在OpenVX中,框架负责缓冲区分配并将此缓冲区地址提供给驱动程序。

3、ISP(VPAC)读取数据内存地址,如何获取呢?

我没明白。缓冲区由OpenVX分配并传递给VPAC..

4、三个独立可同时输出流VPAC、CSI_TX_IF、DMA-NAVSS,是通过什么控制CSI_RX_IF往哪一个流进行输出呢?

当前驱动程序只支持DMA-NAVSS流。所以你可以忽略其他两个流。

如有其他问题,请重新提一个帖子