我想通过AM623来连接16个SPI接口的ADC,要求16路同步采集数据,SPI接口既能够设置ADC,又能读取ADC结果数据,通过A?AM623自带的PRUSS能否实现?SPI时钟速率最大10Mhz即可,不知到它能实现的最大SPI时钟频率是多少?

您好,Lydia,

好的,这将比您可能与客户进行的其他讨论复杂一点,因为这不是简单的"是"或"否"答案。 我们或客户可能需要进行一些原型制作,以确定他们想要做的事情是否可行。

硬件外设接口与模拟外设接口

对于处理器上的硬件外设SPI接口,我们了解SPI接口的局限性,并在处理器数据表中公布这些局限性。 PRU能够控制AM62x上的硬件外围设备(例如SPI或UART)。

PRU内核还可以比特爆炸引脚("比特爆炸"是指软件直接写入以驱动引脚高或低)来模拟SPI等通信协议。 这种能力是使PRU不同于其他处理器内核的超级大国之一。 有关详细信息,请参阅新的普鲁大学研究院主板的"How are PRU GPIO signals different from regular GPIOs?"页面。 (我仍在编写本文档的AM62x版本,因此我现在将链接到AM64x版本)。

在客户考虑编写代码以模拟PRU内核的接口之前,我总是停下来检查是否可以使用现有的硬件外围设备,因为这通常比对接口进行位敲击更容易编程。 实际上,我现在有几个客户希望Linux控制外围设备接口,但该接口的运行频率高于Linux所能处理的频率。 因此,他们正在设计Linux和PRU内核以Linux友好的速度在大型缓冲区中来回传递数据,然后PRU内核负责向高速外设输入和输出数据。

好的,那么PRU内核做什么是合理的呢?

对于AM62x上的PRU子系统,可能无法使用16个10MHz SPI端口。 使用现有的示例代码,看起来我们可以在AM62x版本的PRU子系统上以10MHz的频率连接多达13个SPI端口。 可能有其他实现允许稍微更多的附件。

这是我的思考过程:

我们绝对可以在10MHz下执行6个以上的SPI实例

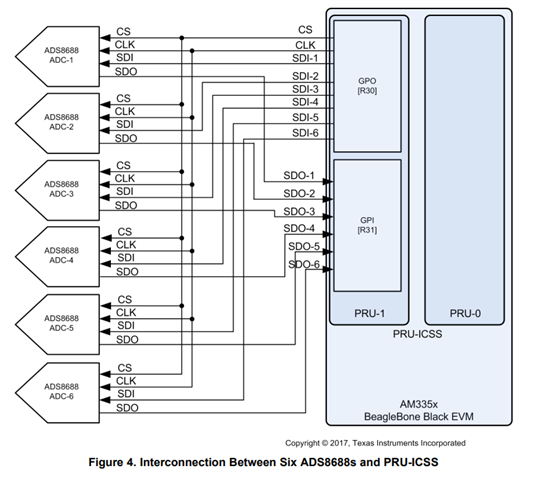

TIDA-01555演示了多达6个ADC通过SPI与PRU子系统进行10MHz通信。The Design guide for this TI design指南非常擅长解释概念,我建议您来看看。 The source code is here.

这种设计是在AM335x上完成的, 内核运行频率为200MHz。 AM62x PRU内核的运行速度高达333MHz,因此AM62x将能够在10MHz时间窗口内执行更多软件指令,并连接到更多的ADC。 根据设计指南的表格"用于连接多个ADC的最大时钟速度",添加额外的ADC似乎会在5ns/clock时增加额外的2个时钟,或6+N*2时钟,其中N是ADC接口的数量。

6个ADC -->11.11MHz -->90ns/5ns =18个时钟

5个ADC -->81ns =16个时钟

4个ADC -->14个时钟

3个ADC -->12个时钟

1个ADC -->8个时钟

因此,如果我们想使用10MHz接口,PRU固件需要能够在100 ns = 33时钟内处理每个接口。

33=6 + N*2 --> N =13.5->该特定项目可以支持13个ADC端口

仅供参考、其他 PRU SPI 工程

对于未来的读者, 我们还有其他几个PRU SPI项目可供您参考。

新的 OpenPRU repo's spi_loopback project

AM64x PRU ADC examples(虽然代码是为AM64x编写的,但固件仅使用PRU内核,因此移植到AM62x相当容易)

我没有提到的另一个注意事项是pinmuxing。 AM62x上的PRU子系统每个PRU内核具有20个GPI和20个GPO信号,因此理论上一个PRU内核可以具有CS,CLK和16个SDI和16个SDO信号(18个输出和16个输入),但我们需要确保没有任何pinmux与处理器针脚上的其他重要信号发生冲突。

从上面列出的设计指南中: