实验室利用6657与FPGA进行PCIE通信,DSP作为RC,FPGA作为EP。

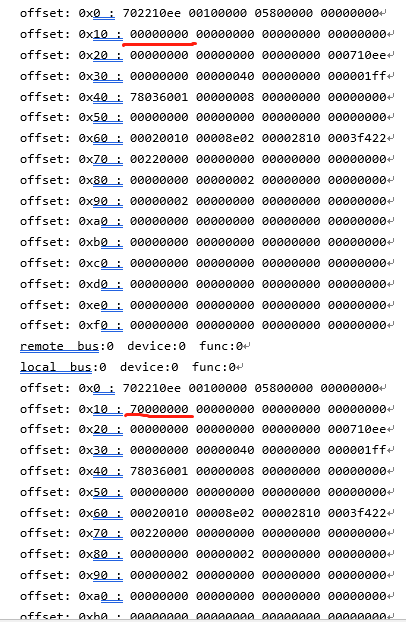

DSP使用的是pdk中的PCIE_exampleProject,在配置EP端bar0基址前后读取0x21802000地址的结果如下:

可以看出EP端,bar0的基地址变为了我设置的0x70000000。

但是我进行以下数据读写操作时:

for (i=0; i<PCIE_BUFSIZE_APP; i++)

{

*((volatile uint32_t *)pcieBase + i) = srcBuf[i];

{

getRegs.debug0 = &debug0;

if (Pcie_readRegs (handle, pcie_LOCATION_LOCAL, &getRegs) != pcie_RET_OK)

{

System_printf ("Read LTSSM state failed!\n");

return;

}

ltssmState = debug0.ltssmState;

System_printf ("Read LTSSM state : %d\n" , ltssmState);

}

System_printf("write the %d-th num, it's %08x\n", i, *((volatile uint32_t *)pcieBase + i));

}

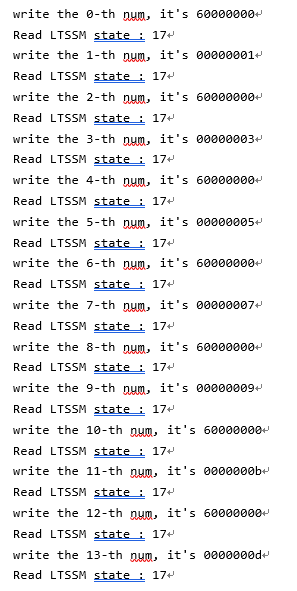

得到的结果并不理想。正确的值应该是0x00—0x37,但是我的结果是下面这样的:

结果是一半一半的,一部分是对的,一部分是错误的。请问这个是因为什么原因?有人遇到类似的问题吗,是如何解决的?