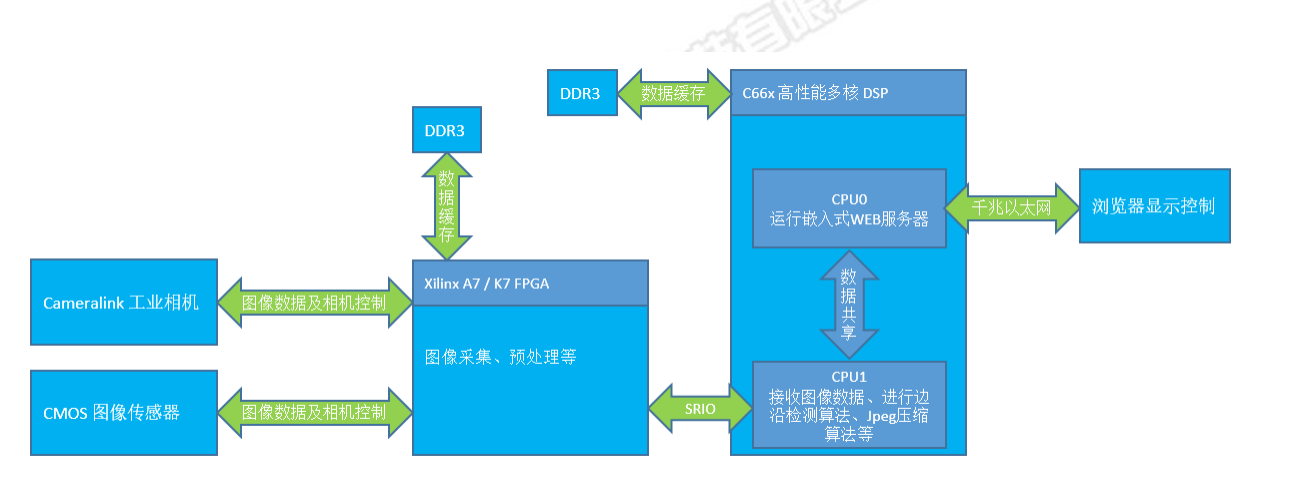

FPGA 对 Cameralink 工业相机数据的采集, FPGA 与 DSP 的高速通讯,以及多核 DSP 如何协同工作。首先 FPGA 采集 Cameralink 工业相机输出的图像数

据并缓存至本地缓存中,当缓存一帧完整的图像后,通过高速 SRIO 接口把图像数据传送 至 DSP 的内存中,传送完 1 帧图像后向 DSP 发送中断以通知 DSP 处理数据。然后多核 DSP会把该中断路由至 Core1, Core1 接收到中断后对原始图像进行边沿检测算法,然后将原始图像和通过边沿检测后的图像合并成一副图像,并调用 JPEG 压缩算法将合成后的图像压缩为 JPEG 格式。 JPEG 压缩完成后,会将 JPEG 格式的图像数据拷贝到 Core0 与 Core1共享的内存中,并且 Core1 会向 Core0 发送 IPC 中断,通知 Core0 处理数据。最后多核DSP 使用 Core0 内建嵌入式 WEB 服务器, PC 机通过浏览器即可方便的查看 JPEG 格式的原始图像和经过算法处理的图像。