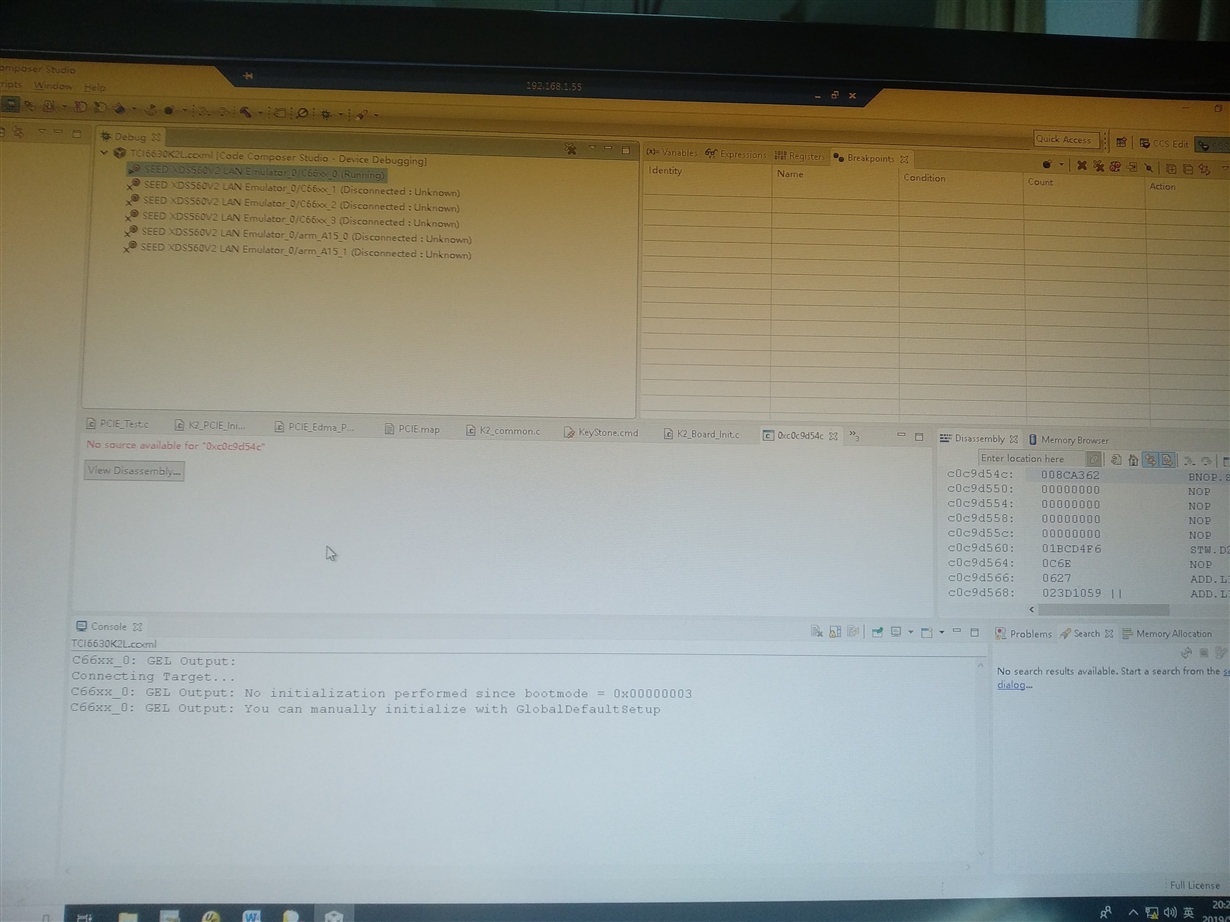

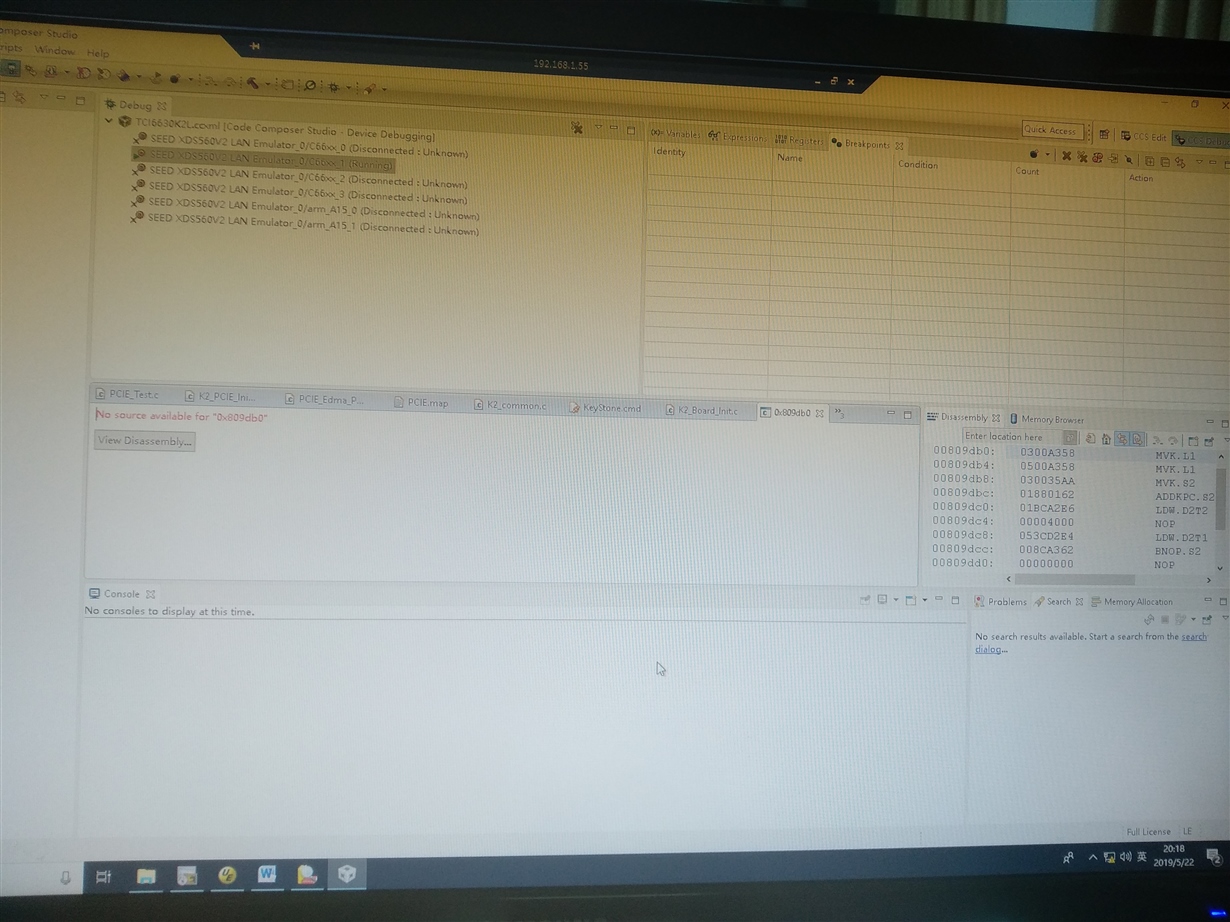

将K2的PCIE的例程加载到自己的板子上6630的板子上,加载core0或是core1的时候,运行的时候没有输出,同时将PCIE.OUT加载到core0和core1,也不行。如图:

1、请问这是内存配置不对吗?

2、我用的是自己的板子6630,通过ARM来激活让DSP核跑起来,从图中可以看出是通过flash 来boot,而例程要求是no boot,是不是因为这个原因导致的?如果是,怎么修改将例程配置为 nand flash 启动?

3、将同一个PCIE.out同时加载到core0和core1,程序是怎么自己识别内核的不同,然后修改设备号device0和device1,然后core0为RC,core1为EP? 是否要修改例程,分别修改为RC和EP,然后在编译分别加载到core0和core1?