6678 的DDR3控制器CS0和CS1各: 接64位宽,5片16位宽DDR,每片512MB(其中一片ECC)

在800MHZ-1000MHZ CS0和CS1 DDR3 CS0和CS1空间测试正常

在1000MHZ---1600MHZ出现如下问题:

CS0的DDR3空间正常

CS1的DDR3高32位读写不正常,低32位读写正常。

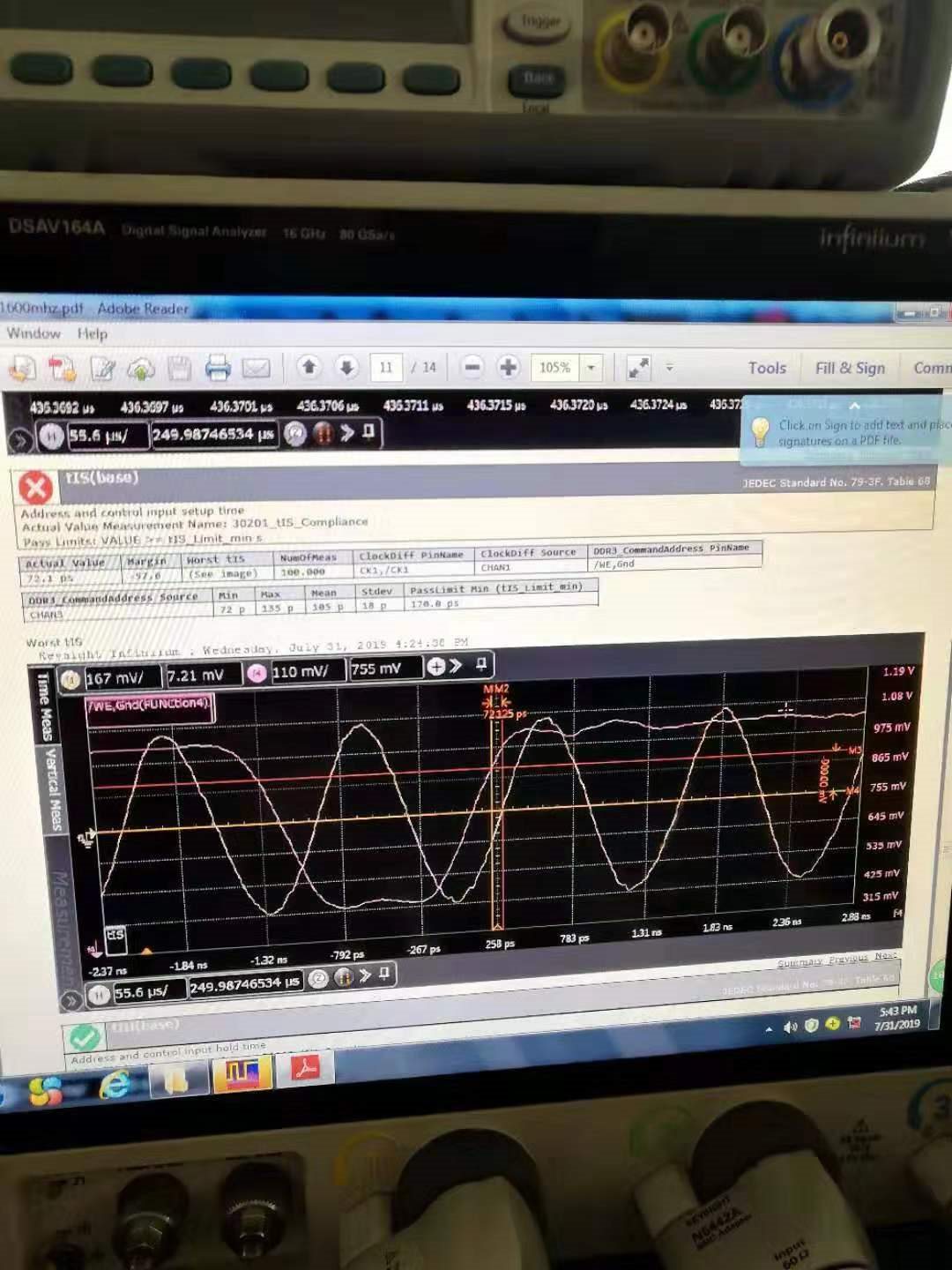

用示波器测量CK1和WE信号在1600MHZ下时序关系比较紧张,请问6678的DDR3控制器通过什么方法来调整时钟和命令线的关系或者有办法调整时钟输出的相位吗?如1/4相位。

下图是WE和CK1这组的关系: