请教个问题:

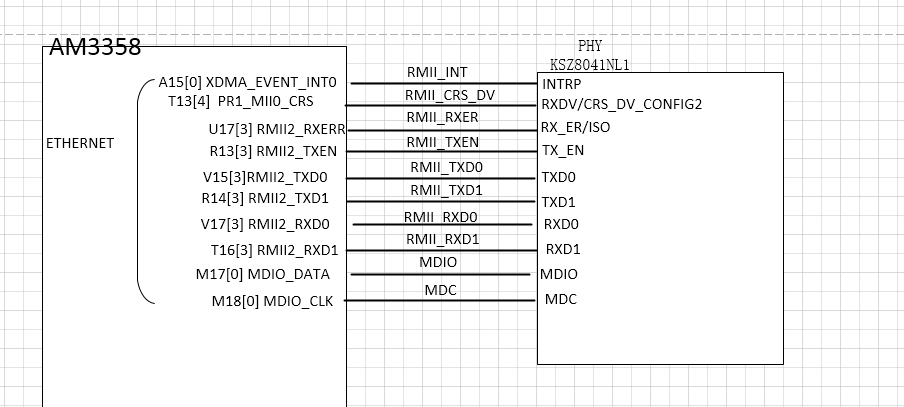

使用AM3358的mii2 连接KSZ8041PHY,在uboot下ping不通?

请教一下在uboot中是否可以使用mii2进行网络通信,需要进行如何设置?

使用的uboot版本为2018.07如图:

uboot中的pinmux的配置为:

static struct module_pin_mux rmii2_pin_mux[] = {

{OFFSET(mdio_clk), MODE(0) | PULLUP_EN}, /* MDIO_CLK */

{OFFSET(mdio_data), MODE(0) | RXACTIVE | PULLUP_EN}, /* MDIO_DATA */

{OFFSET(gpmc_csn3), MODE(2) | RXACTIVE}, /* MII2_CRS *//* gpmc_csn3.rmmii2_crs_dv */

{OFFSET(gpmc_wpn), MODE(3) | RXACTIVE}, /* MII2_RXERR *//* gpmc_wpn.rmmii2_rxer */

{OFFSET(gpmc_a0), MODE(3)}, /* MII2_TXEN */ /* gpmc_a0.rmmii2_txen */

{OFFSET(gpmc_a4), MODE(3)}, /* MII1_TXD1 */ /* gpmc_a4.rmmii2_txd1 */

{OFFSET(gpmc_a5), MODE(3)}, /* MII1_TXD0 */ /* gpmc_a5.rmmii2_txd0 */

{OFFSET(gpmc_a10), MODE(3) | RXACTIVE}, /* MII1_RXD1 *//* gpmc_a10.rmmii2_rxd1 */

{OFFSET(gpmc_a11), MODE(3) | RXACTIVE}, /* MII1_RXD0 *//* gpmc_a11.rmmii2_rxd0 */

{OFFSET(mii1_col), MODE(1) | RXACTIVE}, /* RMII1_REFCLK *//* gpmc_a11.rmmii2_REFCLK */

{-1},

};

dts中的配置为:

/*net*/

cpsw_default: cpsw_default {

pinctrl-single,pins = <

AM33XX_IOPAD(0x840, PIN_OUTPUT_PULLDOWN | MUX_MODE3) /* gpmc_a0.rmmii2_txen */

AM33XX_IOPAD(0x854, PIN_OUTPUT_PULLDOWN | MUX_MODE3) /* gpmc_a5.rmmii2_txd0 */

AM33XX_IOPAD(0x850, PIN_OUTPUT_PULLDOWN | MUX_MODE3) /* gpmc_a4.rmmii2_txd1 */

AM33XX_IOPAD(0x874, PIN_INPUT_PULLDOWN | MUX_MODE3) /* gpmc_wpn.rmmii2_rxer */

AM33XX_IOPAD(0x888, PIN_INPUT_PULLDOWN | MUX_MODE2) /* gpmc_csn3.rmmii2_crs_dv */

AM33XX_IOPAD(0x86c, PIN_INPUT_PULLDOWN | MUX_MODE3) /* gpmc_a11.rmmii2_rxd0 */

AM33XX_IOPAD(0x868, PIN_INPUT_PULLDOWN | MUX_MODE3) /* gpmc_a11.rmmii2_rxd1 */

AM33XX_IOPAD(0x908, PIN_INPUT_PULLDOWN | MUX_MODE1) /* gpmc_a11.rmmii2_REFCLK */

>;

};

davinci_mdio_default: davinci_mdio_default {

pinctrl-single,pins = <

/* MDIO */

AM33XX_IOPAD(0x948, PIN_INPUT_PULLUP | SLEWCTRL_FAST | MUX_MODE0) /* mdio_data.mdio_data */

AM33XX_IOPAD(0x94c, PIN_OUTPUT_PULLUP | MUX_MODE0) /* mdio_clk.mdio_clk */

>;

};

gpio_mdio_default: gpio_mdio_default {

pinctrl-single,pins = <

/* MDIO via GPIO*/

AM33XX_IOPAD(0x948, PIN_INPUT | MUX_MODE7) /* mdio_data.mdio_data GPIO0_0*/

AM33XX_IOPAD(0x94c, PIN_OUTPUT| MUX_MODE7) /* mdio_clk.mdio_clk GPIO0_1 */

>;

};

&mac {

pinctrl-names = "default";

pinctrl-0 = <&cpsw_default>;

slaves = <1>; /* use only one emac if */

status = "okay";

mdio0: gpio {

compatible = "mdio-gpio";

pinctrl-names = "default";

pinctrl-0 = <&gpio_mdio_default>;

#address-cells = <1>;

#size-cells = <0>;

gpios = <&gpio0 1 GPIO_ACTIVE_HIGH /* MDIO-CLK */

&gpio0 0 GPIO_ACTIVE_HIGH>; /* MDIO-DATA */

phy0: ethernet-phy@1 {

reg = <0>;

};

};

};

&davinci_mdio {

pinctrl-names = "default";

pinctrl-0 = <&davinci_mdio_default>;

status = "disabled";

};&cpsw_emac1 {

phy_id = <&mdio0>,<2>;

phy-mode = "rmii";

};

&phy_sel {

rmii-clock-ext;

};

/*

* Copyright (C) 2012 Texas Instruments Incorporated - http://www.ti.com/

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License version 2 as

* published by the Free Software Foundation.

*/

/*

* AM335x Starter Kit

* http://www.ti.com/tool/tmdssk3358

*/

/dts-v1/;

#include "am33xx.dtsi"

#include <dt-bindings/pwm/pwm.h>

#include <dt-bindings/interrupt-controller/irq.h>

/ {

model = "TI AM335x EVM-SK";

compatible = "ti,am335x-evmsk", "ti,am33xx";

chosen {

stdout-path = &uart0;

tick-timer = &timer2;

};

cpus {

cpu@0 {

cpu0-supply = <&vdd1_reg>;

};

};

memory {

device_type = "memory";

reg = <0x80000000 0x40000000>;

};

vbat: fixedregulator@0 {

compatible = "regulator-fixed";

regulator-name = "vbat";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

regulator-boot-on;

};

};

&am33xx_pinmux {

pinctrl-names = "default";

pinctrl-0 = <&clkout2_pin>;

i2c0_pins: pinmux_i2c0_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x988, PIN_INPUT_PULLUP | MUX_MODE0) /* i2c0_sda.i2c0_sda */

AM33XX_IOPAD(0x98c, PIN_INPUT_PULLUP | MUX_MODE0) /* i2c0_scl.i2c0_scl */

>;

};

i2c1_pins: pinmux_i2c1_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x90c, PIN_INPUT_PULLUP | MUX_MODE3) /* i2c1_sda.i2c1_sda */

AM33XX_IOPAD(0x910, PIN_INPUT_PULLUP | MUX_MODE3) /* i2c1_scl.i2c1_scl */

>;

};

uart0_pins: pinmux_uart0_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x970, PIN_INPUT_PULLUP | MUX_MODE0) /* uart0_rxd.uart0_rxd */

AM33XX_IOPAD(0x974, PIN_OUTPUT_PULLDOWN | MUX_MODE0) /* uart0_txd.uart0_txd */

>;

};

clkout2_pin: pinmux_clkout2_pin {

pinctrl-single,pins = <

AM33XX_IOPAD(0x9b4, PIN_OUTPUT_PULLDOWN | MUX_MODE3) /* xdma_event_intr1.clkout2 */

>;

};

/*net*/

cpsw_default: cpsw_default {

pinctrl-single,pins = <

AM33XX_IOPAD(0x840, PIN_OUTPUT_PULLDOWN | MUX_MODE3) /* gpmc_a0.rmmii2_txen */

AM33XX_IOPAD(0x854, PIN_OUTPUT_PULLDOWN | MUX_MODE3) /* gpmc_a5.rmmii2_txd0 */

AM33XX_IOPAD(0x850, PIN_OUTPUT_PULLDOWN | MUX_MODE3) /* gpmc_a4.rmmii2_txd1 */

AM33XX_IOPAD(0x874, PIN_INPUT_PULLDOWN | MUX_MODE3) /* gpmc_wpn.rmmii2_rxer */

AM33XX_IOPAD(0x888, PIN_INPUT_PULLDOWN | MUX_MODE2) /* gpmc_csn3.rmmii2_crs_dv */

AM33XX_IOPAD(0x86c, PIN_INPUT_PULLDOWN | MUX_MODE3) /* gpmc_a11.rmmii2_rxd0 */

AM33XX_IOPAD(0x868, PIN_INPUT_PULLDOWN | MUX_MODE3) /* gpmc_a11.rmmii2_rxd1 */

AM33XX_IOPAD(0x908, PIN_INPUT_PULLDOWN | MUX_MODE1) /* gpmc_a11.rmmii2_REFCLK */

>;

};

davinci_mdio_default: davinci_mdio_default {

pinctrl-single,pins = <

/* MDIO */

AM33XX_IOPAD(0x948, PIN_INPUT_PULLUP | SLEWCTRL_FAST | MUX_MODE0) /* mdio_data.mdio_data */

AM33XX_IOPAD(0x94c, PIN_OUTPUT_PULLUP | MUX_MODE0) /* mdio_clk.mdio_clk */

>;

};

gpio_mdio_default: gpio_mdio_default {

pinctrl-single,pins = <

/* MDIO via GPIO*/

AM33XX_IOPAD(0x948, PIN_INPUT | MUX_MODE7) /* mdio_data.mdio_data GPIO0_0*/

AM33XX_IOPAD(0x94c, PIN_OUTPUT| MUX_MODE7) /* mdio_clk.mdio_clk GPIO0_1 */

>;

};

mmc2_pins: pinmux_mmc2_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x928, PIN_INPUT_PULLUP | MUX_MODE6) /* MII1_TXD0.mmc1_clk */

AM33XX_IOPAD(0x924, PIN_INPUT_PULLUP | MUX_MODE6) /* gmii1_txd1.mmc1_cmd */

AM33XX_IOPAD(0x92C, PIN_INPUT_PULLUP | MUX_MODE4) /* gmii1_txclk.mmc1_dat0 */

AM33XX_IOPAD(0x930, PIN_INPUT_PULLUP | MUX_MODE4) /* gmii1_rxclk.mmc1_dat1 */

AM33XX_IOPAD(0x934, PIN_INPUT_PULLUP | MUX_MODE4) /* gmii1_rxd3.mmc1_dat2 */

AM33XX_IOPAD(0x938, PIN_INPUT_PULLUP | MUX_MODE4) /* gmii1_rxd2.mmc1_dat3 */

>;

};

nandflash_pins_s0: nandflash_pins_s0 {

pinctrl-single,pins = <

AM33XX_IOPAD(0x800, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad0.gpmc_ad0 */

AM33XX_IOPAD(0x804, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad1.gpmc_ad1 */

AM33XX_IOPAD(0x808, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad2.gpmc_ad2 */

AM33XX_IOPAD(0x80c, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad3.gpmc_ad3 */

AM33XX_IOPAD(0x810, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad4.gpmc_ad4 */

AM33XX_IOPAD(0x814, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad5.gpmc_ad5 */

AM33XX_IOPAD(0x818, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad6.gpmc_ad6 */

AM33XX_IOPAD(0x81c, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_ad7.gpmc_ad7 */

AM33XX_IOPAD(0x870, (PIN_INPUT_PULLUP | MUX_MODE0)) /* gpmc_wait0.gpmc_wait0 */

AM33XX_IOPAD(0x87c, (PIN_OUTPUT | MUX_MODE0)) /* gpmc_csn0.gpmc_csn0 */

AM33XX_IOPAD(0x890, (PIN_OUTPUT | MUX_MODE0)) /* gpmc_advn_ale.gpmc_advn_ale */

AM33XX_IOPAD(0x894, (PIN_OUTPUT | MUX_MODE0)) /* gpmc_oen_ren.gpmc_oen_ren */

AM33XX_IOPAD(0x898, (PIN_OUTPUT | MUX_MODE0)) /* gpmc_wen.gpmc_wen */

AM33XX_IOPAD(0x89c, (PIN_OUTPUT | MUX_MODE0)) /* gpmc_be0n_cle.gpmc_be0n_cle */

>;

};

spi0_pins: pinmux_spi0_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x150, (PIN_INPUT_PULLDOWN | MUX_MODE0)) /* spi0_sclk.spi0_sclk */

AM33XX_IOPAD(0x154, (PIN_INPUT_PULLUP | MUX_MODE0)) /* spi0_d0.spi0_d0 */

AM33XX_IOPAD(0x158, (PIN_INPUT_PULLDOWN | MUX_MODE0)) /* spi0_d1.spi0_d1 */

AM33XX_IOPAD(0x15c, (PIN_INPUT_PULLUP | MUX_MODE0)) /* spi0_CS0.spi0_CS0 */

>;

};

spi1_pins: pinmux_spi1_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x190, (PIN_INPUT_PULLDOWN | MUX_MODE3)) /* spi1_sclk.spi1_sclk */

AM33XX_IOPAD(0x194, (PIN_INPUT_PULLUP | MUX_MODE3)) /* spi1_d0.spi1_d0 */

AM33XX_IOPAD(0x198, (PIN_INPUT_PULLDOWN | MUX_MODE3)) /* spi1_d1.spi1_d1 */

AM33XX_IOPAD(0x19c, (PIN_INPUT_PULLUP | MUX_MODE3)) /* spi1_CS0.spi1_CS0 */

>;

};

dcan0_pins: pinmux_dcan0_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x968, PIN_OUTPUT | MUX_MODE2) /* uart0_ctsn.d_can1_tx */

AM33XX_IOPAD(0x96c, PIN_INPUT_PULLDOWN | MUX_MODE2) /* uart0_rtsn.d_can1_rx */

>;

};

dcan1_pins: pinmux_dcan0_pins {

pinctrl-single,pins = <

AM33XX_IOPAD(0x91c, PIN_OUTPUT | MUX_MODE1) /* gmii1_txd2.d_can0_tx */

AM33XX_IOPAD(0x920, PIN_INPUT_PULLDOWN | MUX_MODE1) /* gmii1_rxd2.d_can0_rx */

>;

};

};

&uart0 {

pinctrl-names = "default";

pinctrl-0 = <&uart0_pins>;

status = "okay";

};

&i2c0 {

pinctrl-names = "default";

pinctrl-0 = <&i2c0_pins>;

status = "okay";

clock-frequency = <400000>;

tps: tps@2d {

reg = <0x2d>;

};

};

&usb {

status = "okay";

};

&usb_ctrl_mod {

status = "okay";

};

&usb0_phy {

status = "okay";

};

&usb1_phy {

status = "okay";

};

&usb0 {

status = "okay";

};

&usb1 {

status = "okay";

dr_mode = "host";

};

#include "tps65910.dtsi"

&tps {

vcc1-supply = <&vbat>;

vcc2-supply = <&vbat>;

vcc3-supply = <&vbat>;

vcc4-supply = <&vbat>;

vcc5-supply = <&vbat>;

vcc6-supply = <&vbat>;

vcc7-supply = <&vbat>;

vccio-supply = <&vbat>;

regulators {

vrtc_reg: regulator@0 {

regulator-always-on;

};

vio_reg: regulator@1 {

regulator-always-on;

};

vdd1_reg: regulator@2 {

/* VDD_MPU voltage limits 0.95V - 1.26V with +/-4% tolerance */

regulator-name = "vdd_mpu";

regulator-min-microvolt = <912500>;

regulator-max-microvolt = <1312500>;

regulator-boot-on;

regulator-always-on;

};

vdd2_reg: regulator@3 {

/* VDD_CORE voltage limits 0.95V - 1.1V with +/-4% tolerance */

regulator-name = "vdd_core";

regulator-min-microvolt = <912500>;

regulator-max-microvolt = <1150000>;

regulator-boot-on;

regulator-always-on;

};

vdd3_reg: regulator@4 {

regulator-always-on;

};

vdig1_reg: regulator@5 {

regulator-always-on;

};

vdig2_reg: regulator@6 {

regulator-always-on;

};

vpll_reg: regulator@7 {

regulator-always-on;

};

vdac_reg: regulator@8 {

regulator-always-on;

};

vaux1_reg: regulator@9 {

regulator-always-on;

};

vaux2_reg: regulator@10 {

regulator-always-on;

};

vaux33_reg: regulator@11 {

regulator-always-on;

};

vmmc_reg: regulator@12 {

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

};

};

};

&mac {

pinctrl-names = "default";

pinctrl-0 = <&cpsw_default>;

slaves = <1>; /* use only one emac if */

status = "okay";

mdio0: gpio {

compatible = "mdio-gpio";

pinctrl-names = "default";

pinctrl-0 = <&gpio_mdio_default>;

#address-cells = <1>;

#size-cells = <0>;

gpios = <&gpio0 1 GPIO_ACTIVE_HIGH /* MDIO-CLK */

&gpio0 0 GPIO_ACTIVE_HIGH>; /* MDIO-DATA */

phy0: ethernet-phy@1 {

reg = <0>;

};

};

};

&davinci_mdio {

pinctrl-names = "default";

pinctrl-0 = <&davinci_mdio_default>;

status = "disabled";

};

&cpsw_emac1 {

phy_id = <&mdio0>,<2>;

phy-mode = "rmii";

};

&phy_sel {

rmii-clock-ext;

};

&sham {

status = "okay";

};

&aes {

status = "okay";

};

&tscadc {

status = "okay";

tsc {

ti,wires = <4>;

ti,x-plate-resistance = <200>;

ti,coordinate-readouts = <5>;

ti,wire-config = <0x00 0x11 0x22 0x33>;

};

};

&elm {

status = "okay";

};

&gpmc {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&nandflash_pins_s0>;

ranges = <0 0 0x08000000 0x10000000>; /* CS0: 128MB for NAND */

nand@0,0 {

reg = <0 0 0>; /* CS0, offset 0, IO size 4 */

ti,nand-ecc-opt = "bch8";

ti,elm-id = <&elm>;

nand-bus-width = <8>;

gpmc,device-width = <1>;

gpmc,sync-clk-ps = <0>;

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <44>;

gpmc,cs-wr-off-ns = <44>;

gpmc,adv-on-ns = <6>;

gpmc,adv-rd-off-ns = <34>;

gpmc,adv-wr-off-ns = <44>;

gpmc,we-on-ns = <0>;

gpmc,we-off-ns = <40>;

gpmc,oe-on-ns = <0>;

gpmc,oe-off-ns = <54>;

gpmc,access-ns = <64>;

gpmc,rd-cycle-ns = <82>;

gpmc,wr-cycle-ns = <82>;

gpmc,wait-on-read = "true";

gpmc,wait-on-write = "true";

gpmc,bus-turnaround-ns = <0>;

gpmc,cycle2cycle-delay-ns = <0>;

gpmc,clk-activation-ns = <0>;

gpmc,wait-monitoring-ns = <0>;

gpmc,wr-access-ns = <40>;

gpmc,wr-data-mux-bus-ns = <0>;

/* MTD partition table */

/* All SPL-* partitions are sized to minimal length

* which can be independently programmable. For

* NAND flash this is equal to size of erase-block */

#address-cells = <1>;

#size-cells = <1>;

partition@0 {

label = "NAND.SPL";

reg = <0x00000000 0x000020000>;

};

partition@1 {

label = "NAND.SPL.backup1";

reg = <0x00020000 0x00020000>;

};

partition@2 {

label = "NAND.SPL.backup2";

reg = <0x00040000 0x00020000>;

};

partition@3 {

label = "NAND.SPL.backup3";

reg = <0x00060000 0x00020000>;

};

partition@4 {

label = "NAND.u-boot-spl-os";

reg = <0x00080000 0x00040000>;

};

partition@5 {

label = "NAND.u-boot";

reg = <0x000C0000 0x00100000>;

};

partition@6 {

label = "NAND.u-boot-env";

reg = <0x001C0000 0x00020000>;

};

partition@7 {

label = "NAND.u-boot-env.backup1";

reg = <0x001E0000 0x00020000>;

};

partition@8 {

label = "NAND.kernel";

reg = <0x00200000 0x00800000>;

};

partition@9 {

label = "NAND.file-system";

reg = <0x00A00000 0x0F600000>;

};

};

};

&spi0 {

pinctrl-names = "default";

pinctrl-0 = <&spi0_pins>;

status = "okay";

spi-flash@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "mx25l25635e";

reg = <0>; /* Chip select 0 */

spi-max-frequency = <24000000>;

partition@0 {

label = "dummy";

reg = <0x0000000 0x8000>;

};

};

};

&spi1 {

pinctrl-names = "default";

pinctrl-0 = <&spi1_pins>;

status = "okay";

};

&mmc2 {

status = "okay";

vmmc-supply = <&vmmc_reg>;

bus-width = <4>;

pinctrl-names = "default";

pinctrl-0 = <&mmc2_pins>;

non-removable;

};

&dcan0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&dcan0_pins>;

};

&dcan1 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&dcan1_pins>;

};