我在调试DSP(C6748)通过EMIF与FPGA进行数据读写时遇到一些问题,需要你们的技术支持!

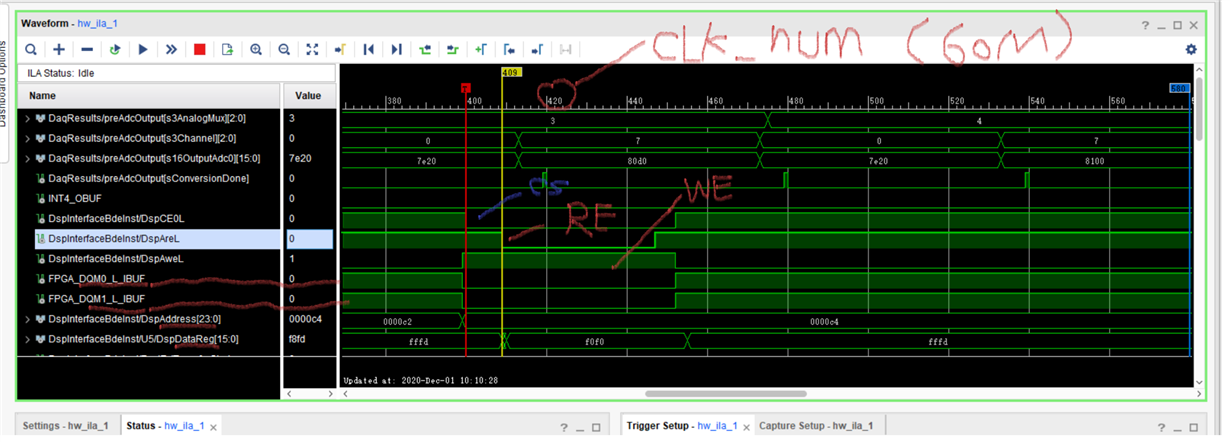

我把测试case简化为: 在DSP 的12KHZ主中断中读取FPGA片选信号(CS2)所映射的地址范围中的一个地址的值,然后查看对应的时序图,如下图,

其中最上面的数字表示60M的CLK的数量,可以作为时间参考,接下来按照标记依次为:片选信号CE,读使能信号OE,写使能信号WE,地址总线,数据总线。

关于这个时序图我有几个问题想请教下:

- 地址总线上地址在整个读周期结束(CS拉高)后还一直持续的可能原因有哪些,主要是我自己不知道是不是哪里配置出错?

- 整个读操作的周期持续了近50个CLK(60M),远远大于在对EMIF控制寄存器进行配置的(Setup+strobe+hold=2+3+2)7个CLK数量的可能原因有哪些?

时序图:

为了方便分析,我把EMIF初始化配置截图一下:

想问问大家是哪里配置错误还是漏掉什么了吗?