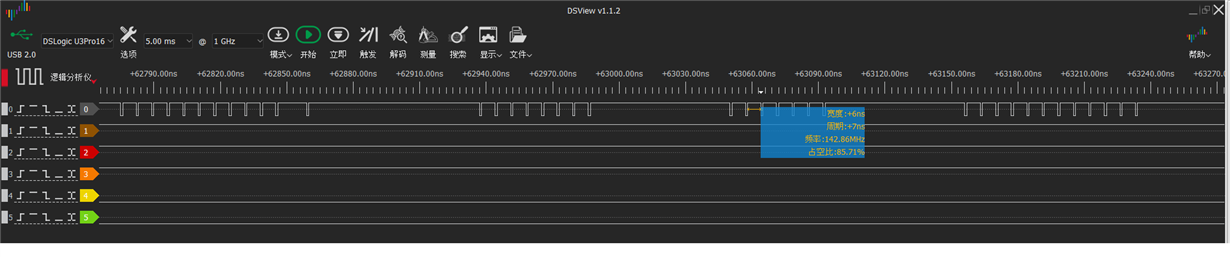

外部晶振为25MHz,在C6748中想把EMIFA的时钟设置到130-148MHz的告诉水平,同时不想主频低于400MHz,于是在PLL中将倍频系数设置为16(实际主频就等于17*25MHz=425MHz),并将PPL0中的SYSCLK3分频系数设置为2(理论输出是425/3=141MHz),这个给EMIF用,那么EMIFA的时钟理论上就是141MHZ(低于EMIFA最大的148MHZ),但实际用1GHz带宽的逻辑分析仪测试这个时钟信号发现,这个时钟信号偶尔是141MHz左右,但大部分时钟信号的频率是乱的(远低于141M),如下图所示。

想请问下这是什么原因?