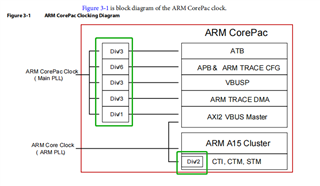

请问TI各位老师,下图中的Div/1、Div/2、Div/3、Div/6是由寄存器配置的吗?如果是,哪是由那些寄存器配置的?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

谢谢Nancy Wang回复,感觉不太像是通过PLLDIV来配置的,PLLDIV是PLL模块中的功能,而图里说是ARM核内的

图片来自

KeyStone II Architecture ARM CorePac User Guide

Literature Number: SPRUHJ4

3.2 Clock and Reset

从datasheet描述应该是将sysclk1直接除以系数进行分频。

谢谢Nancy Wang回复,这个datasheet的意思是这个由硬件直接进行分频的,用户没法通过寄存器进行配置,对吗?

结合以下表格和帖子看了一下,应该还是通过PLLDIV来配置的。表格或者是框图只是说明各个模块使用哪个时钟分频,最终还是通过main PLL来配置。

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/755583/66ak2h12-register-setting-internal-clock-divider-s-and-shared-local-clock-divider