我查阅Application report ZHCA575 TMS320C6678存储器访问性能后产生了些疑问想确认一下。

由于6678的存储器结构,越往外的存储器容量越大,但是速率低。那么把数据放到共享内存上进行处理和把数据放到ddr上处理的耗时应该是不一样的,并且放在共享内存上进行处理应该更快。

而Cache可解决core时钟与L2 SL2 DDR这几个存储器时钟不匹配的问题。那么我使用CACHE_enableCaching语句和CACHE_setLxxSize语句,将ddr地址进行映射。因为设置了cache,那么在ddr上处理数据的速度应该会有提高。

我进行了测试发现,这个逻辑好像是对的,但又不敢确定,所以想来确认一下。请问这个逻辑和实验结果是合理的吗?

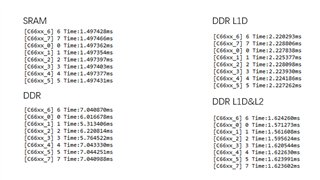

上面是分别在sram、ddr、ddr(使能L1Dcache)、ddr(使能L1D、L2cache)内存空间上进行的测试结果。