使用C6678和FPGA通过SRIO进行数据发送 ,使用NWRITE类型包,我的destaddr如果写八的倍数时例如(0x40000008),FPGA侧可以收到正确的地址,但是如果我destaddr不是八的倍数,FPGA侧收到的地址就会有偏移,例如 DSP侧destaddr是0x40000004,FPGA收到的地址将会是0x40000004。我想知道这个是因为协议自身的规则吗。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

使用C6678和FPGA通过SRIO进行数据发送 ,使用NWRITE类型包,我的destaddr如果写八的倍数时例如(0x40000008),FPGA侧可以收到正确的地址,但是如果我destaddr不是八的倍数,FPGA侧收到的地址就会有偏移,例如 DSP侧destaddr是0x40000004,FPGA收到的地址将会是0x40000004。我想知道这个是因为协议自身的规则吗。

FPGA侧收到的地址就会有偏移,例如 DSP侧destaddr是0x40000004,FPGA收到的地址将会是0x40000004。

请问是如何偏移的?

我看文档中写的是 when the Byte_Count of Read/Write requests exceeds 256Bytes. Second, when Read/Write request RapidIO address is non-64b aligned. In both cases, the outgoing request must be broken up into multiple RapidIO request packets ,这里意思是destaddr地址必须是64b对其 意思是 destaddr要是8的倍数吗

问题最终找到了原因 : 由于FPGA AXI4-Stream协议中tdata信号为8个字节,也就是一个双字(Double Word),所以Size域的值需要分两种情况讨论:传输的数据量小于8字节和传输的数据量大于8字节。

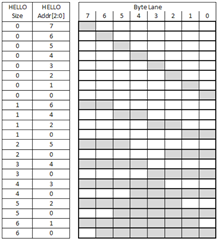

传输的数据量小于8字节(Sub-DWORD Accesses):

对于传输的数据量小于8字节的情况,address字段和size字段用来决定有效的字节位置(tkeep信号必须为0xff),但是仅仅能导致RapidIO包中rdsize/wrsize和wdptr为有效值的address和size值组合才是被允许的,下图是HELLO格式中address和size两个字段与有效字节位置的对应关系示意图(图中灰色部分为有效字节位置)