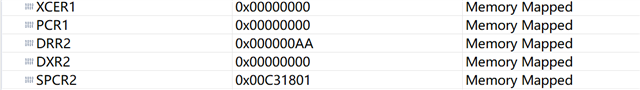

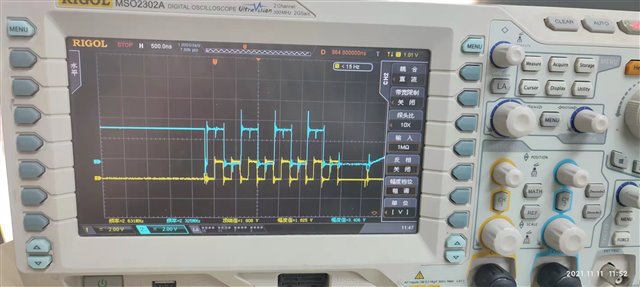

你好,c6416的mcbsp配置为spi从机模式,在发送两个字节后,spcr的发送位就置不了1了,主机那边是while(1)里面先发送一个字节再读取一个字节可以量到一直有时钟,从机6416也是while(1)里面一直发送一个字节通过debug走了两圈就停下了spcr的值0x00C51801 第17位xrdy置不了1,下面是我的6416从机配置

static MCBSP_Config MyMcbspConfig =

{

MCBSP_SPCR_RMK //Serial Port Control Register (SPCR)

(

MCBSP_SPCR_FREE_DEFAULT, // Serial clock free running mode(FREE)

MCBSP_SPCR_SOFT_DEFAULT, // Serial clock emulation mode(SOFT)

MCBSP_SPCR_FRST_DEFAULT, // Frame sync generator reset(FRST)

MCBSP_SPCR_GRST_DEFAULT, // Sample rate generator reset(GRST)

MCBSP_SPCR_XINTM_DEFAULT, // Transmit interrupt mode(XINTM)

MCBSP_SPCR_XSYNCERR_DEFAULT, // Transmit synchronization error

MCBSP_SPCR_XRST_DEFAULT, // Transmitter reset(XRST)

MCBSP_SPCR_DLB_DEFAULT, // Digital loopback(DLB) mode

MCBSP_SPCR_RJUST_DEFAULT, // Receive data sign-extension and

// justification mode(RJUST)

MCBSP_SPCR_CLKSTP_DELAY, // Clock stop(CLKSTP) mode

MCBSP_SPCR_DXENA_OFF, // DX Enabler(DXENA) -Extra delay for

// DX turn-on time.

MCBSP_SPCR_RINTM_DEFAULT, // Receive interrupt(RINT) mode

MCBSP_SPCR_RSYNCERR_DEFAULT, // Receive synchronization error(RSYNCERR)

MCBSP_SPCR_RRST_DEFAULT // Receiver reset(RRST)

),

MCBSP_RCR_RMK // Receive Control Register (RCR)

(

MCBSP_RCR_RPHASE_SINGLE, // Receive phases

MCBSP_RCR_RFRLEN2_OF(0), // Receive frame length

// in phase 2(RFRLEN2)

MCBSP_RCR_RWDLEN2_8BIT, // Receive element length

// in phase 2(RWDLEN2)

MCBSP_RCR_RCOMPAND_MSB, // Receive companding mode (RCOMPAND)

MCBSP_RCR_RFIG_NO, // Receive frame ignore(RFIG)

MCBSP_RCR_RDATDLY_0BIT, // Receive data delay(RDATDLY)

MCBSP_RCR_RFRLEN1_OF(0), // Receive frame length

// in phase 1(RFRLEN1)

MCBSP_RCR_RWDLEN1_8BIT, // Receive element length

// in phase 1(RWDLEN1)

MCBSP_RCR_RWDREVRS_DISABLE // Receive 32-bit bit reversal

// feature.(RWDREVRS)

),

MCBSP_XCR_RMK //Transmit Control Register (XCR)

(

MCBSP_XCR_XPHASE_DEFAULT, // Transmit phases

MCBSP_XCR_XFRLEN2_OF(0), // Transmit frame length

// in phase 2(XFRLEN2)

MCBSP_XCR_XWDLEN2_8BIT, // Transmit element length

// in phase 2

MCBSP_XCR_XCOMPAND_DEFAULT, // Transmit companding mode(XCOMPAND)

MCBSP_XCR_XFIG_DEFAULT, // Transmit frame ignore(XFIG)

MCBSP_XCR_XDATDLY_0BIT, // Transmit data delay(XDATDLY)

MCBSP_XCR_XFRLEN1_OF(0), // Transmit frame length

// in phase 1(XFRLEN1)

MCBSP_XCR_XWDLEN1_8BIT, // Transmit element length

// in phase 1(XWDLEN1)

MCBSP_XCR_XWDREVRS_DISABLE // Transmit 32-bit bit reversal feature

),

MCBSP_SRGR_RMK //serial port sample rate generator register(SRGR)

(

MCBSP_SRGR_GSYNC_FREE, // Sample rate generator clock

// synchronization(GSYNC).

MCBSP_SRGR_CLKSP_RISING, // CLKS polarity clock edge select(CLKSP)

MCBSP_SRGR_CLKSM_INTERNAL, // MCBSP sample rate generator clock

// mode(CLKSM)

MCBSP_SRGR_FSGM_DEFAULT, // Sample rate generator transmit frame

// synchronization

MCBSP_SRGR_FPER_DEFAULT, // Frame period(FPER)

MCBSP_SRGR_FWID_DEFAULT, // Frame width(FWID)

MCBSP_SRGR_CLKGDV_OF(0) // Sample rate generator clock

// divider(CLKGDV)

),

//MCBSP_SRGR_DEFAULT,

MCBSP_MCR_DEFAULT, // Using default value of MCR register

MCBSP_RCERE0_DEFAULT, // Using default value of RCERE registers

MCBSP_RCERE1_DEFAULT,

MCBSP_RCERE2_DEFAULT,

MCBSP_RCERE3_DEFAULT,

MCBSP_XCERE0_DEFAULT, // Using default value of XCERE registers

MCBSP_XCERE1_DEFAULT,

MCBSP_XCERE2_DEFAULT,

MCBSP_XCERE3_DEFAULT,

MCBSP_PCR_RMK //serial port pin control register(PCR)

(

MCBSP_PCR_XIOEN_SP, // Transmitter in general-purpose I/O mode

MCBSP_PCR_RIOEN_SP, // Receiver in general-purpose I/O mode

MCBSP_PCR_FSXM_EXTERNAL, // Transmit frame synchronization mode

MCBSP_PCR_FSRM_EXTERNAL, // Receive frame synchronization mode

MCBSP_PCR_CLKXM_INPUT, // Transmitter clock mode (CLKXM)

MCBSP_PCR_CLKRM_INPUT, // Receiver clock mode (CLKRM)

MCBSP_PCR_CLKSSTAT_0, // CLKS pin status(CLKSSTAT)

MCBSP_PCR_DXSTAT_0, // DX pin status(DXSTAT)

MCBSP_PCR_FSXP_ACTIVELOW, // Transmit frame synchronization polarity(FSXP)

MCBSP_PCR_FSRP_ACTIVELOW, // Receive frame synchronization polarity(FSRP)

MCBSP_PCR_CLKXP_RISING, // Transmit clock polarity(CLKXP)

MCBSP_PCR_CLKRP_FALLING // Receive clock polarity(CLKRP)

)

};

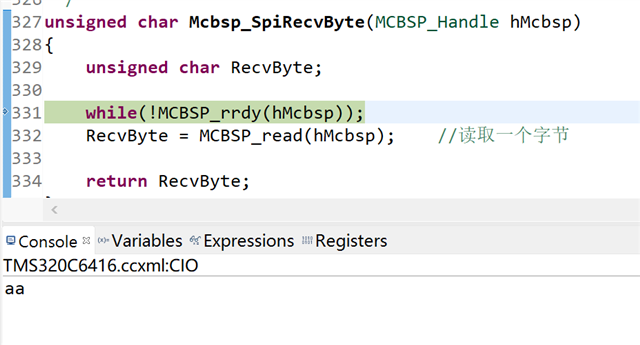

6416这边读到一个后就卡到这了

6416这边读到一个后就卡到这了