各位好:

和大家请教下TDA3的问题。我之前设计的TDA3板回板了,这两天刚开始软硬件联调。过程中遇到些问题,想请教下。

使用CCS Debug,但上来就碰到个问题,Device is locked up in Hard Fault or in NMI. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.4.0.00129),字面意思应该是硬件错误。我复测了下复位,我的板子上仅使用了硬件上电复位,软复位引脚是拉高的。另外尝试把JTAG的TCK降频到1MHz,但还是报相同的问题。最后还是怀疑配置开关SYSBOOT15-0。附下log记录,有很多timeout的地方。

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence In Progress... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence DONE! <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence In Progress... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence DONE! <<<---

ARP32_EVE_1: GEL Output: --->>> Configuring EVE Memory Map <<<---

ARP32_EVE_1: GEL Output: --->>> EVE Memory Map Done! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Target Connect Sequence Begins ... <<<---

Cortex_M4_IPU1_C0: GEL Output: Core Reset has occurred.

Cortex_M4_IPU1_C0: GEL Output: --->>> A device reset occurred <<<---

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx PG3.0 device detected =========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx GP Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx 15x15 Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: Core Reset has occurred.

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx PG3.0 device detected =========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx GP Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx 15x15 Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: --->>> All Control module lock registers are UNLOCKED <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> Changing RTI1 reaction type to avoid RTI1 resetting the device after 3 minutes... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> Starting IPU A-MMU configurations... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> IPU A-MMU configuration completed. <<<---

Cortex_M4_IPU1_C0: GEL Output: ------------------------------------------------------------------------------------------

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR and DPLL configuration Based on Package selection pin status(Sysboot[7]) <<<---

Cortex_M4_IPU1_C0: GEL Output: ------------------------------------------------------------------------------------------

Cortex_M4_IPU1_C0: GEL Output: --->>> 15x15 Package Detected(SYSBOOT[7]=0)... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Clock Configuration for OPPNOM in progress... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> CORE DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> CORE DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> PER DPLL OPP 0 clock config in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> PER DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> DSP_GMAC DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> DSP_GMAC DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> EVE_VID_DSP DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> EVE_VID_DSP_DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Clock Configuration for OPP 0 is DONE! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Configuration for all modules in progress... <<<---

Cortex_M4_IPU1_C0: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C0: GEL Output: module_offset: 0x000000C8

Cortex_M4_IPU1_C0: GEL Output: TIMEOUT

Cortex_M4_IPU1_C0: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C0: GEL Output: module_offset: 0x000000D0

Cortex_M4_IPU1_C0: GEL Output: TIMEOUT

Cortex_M4_IPU1_C0: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C0: GEL Output: module_offset: 0x000000D8

Cortex_M4_IPU1_C0: GEL Output: TIMEOUT

Cortex_M4_IPU1_C0: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C0: GEL Output: module_offset: 0x00000130

Cortex_M4_IPU1_C0: GEL Output: TIMEOUT

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Configuration for all modules is DONE! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR3 initialization starts (TI 15x15 EVM)... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR3 Initialization is in progress ... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR DPLL clock config for 532MHz is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR DPLL clock config for 532MHz is in DONE!

Cortex_M4_IPU1_C0: GEL Output: Launch full leveling

Cortex_M4_IPU1_C0: GEL Output: Updating slave ratios in PHY_STATUSx registers

Cortex_M4_IPU1_C0: GEL Output: as per HW leveling output

Cortex_M4_IPU1_C0: GEL Output: HW leveling is now disabled. Using slave ratios from

Cortex_M4_IPU1_C0: GEL Output: PHY_STATUSx registers

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR3 532MHz Initialization is DONE! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Target Connect Sequence DONE !!!!! <<<---

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: GEL Output: For STM based tracing on TI EVMs,

Cortex_M4_IPU1_C0: GEL Output: run 'TDA3x EVM I2C EXPANDER CONTROL -> Enable_Trace_Pins()' function from Scripts menu on M4/CS_DAP_DebugSS

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: Can't Run Target CPU: (Error -1268 @ 0x1090001) Device is locked up in Hard Fault or in NMI. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.4.0.00129)

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Target Connect Sequence Begins ... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> A device reset occurred <<<---

Cortex_M4_IPU1_C1: GEL Output: ==================================================

Cortex_M4_IPU1_C1: GEL Output: ========= TDA3xx PG3.0 device detected =========

Cortex_M4_IPU1_C1: GEL Output: ========= TDA3xx GP Device detected ===========

Cortex_M4_IPU1_C1: GEL Output: ========= TDA3xx 15x15 Device detected ===========

Cortex_M4_IPU1_C1: GEL Output: ==================================================

Cortex_M4_IPU1_C1: GEL Output: Core Reset has occurred.

Cortex_M4_IPU1_C1: GEL Output: ==================================================

Cortex_M4_IPU1_C1: GEL Output: ========= TDA3xx PG3.0 device detected =========

Cortex_M4_IPU1_C1: GEL Output: ========= TDA3xx GP Device detected ===========

Cortex_M4_IPU1_C1: GEL Output: ========= TDA3xx 15x15 Device detected ===========

Cortex_M4_IPU1_C1: GEL Output: ==================================================

Cortex_M4_IPU1_C1: GEL Output: --->>> All Control module lock registers are UNLOCKED <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> Changing RTI1 reaction type to avoid RTI1 resetting the device after 3 minutes... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> Starting IPU A-MMU configurations... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> IPU A-MMU configuration completed. <<<---

Cortex_M4_IPU1_C1: GEL Output: ------------------------------------------------------------------------------------------

Cortex_M4_IPU1_C1: GEL Output: --->>> DDR and DPLL configuration Based on Package selection pin status(Sysboot[7]) <<<---

Cortex_M4_IPU1_C1: GEL Output: ------------------------------------------------------------------------------------------

Cortex_M4_IPU1_C1: GEL Output: --->>> 15x15 Package Detected(SYSBOOT[7]=0)... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> PRCM Clock Configuration for OPPNOM in progress... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> CORE DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C1: GEL Output: --->>> CORE DPLL OPP already locked, now unlocking....

Cortex_M4_IPU1_C1: GEL Output: --->>> CORE DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C1: GEL Output: --->>> PER DPLL OPP 0 clock config in progress...

Cortex_M4_IPU1_C1: GEL Output: --->>> PER DPLL already locked, now unlocking

Cortex_M4_IPU1_C1: GEL Output: --->>> PER DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C1: GEL Output: --->>> DSP_GMAC DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C1: GEL Output: --->>> DSP_GMAC DPLL already locked, now unlocking....

Cortex_M4_IPU1_C1: GEL Output: --->>> DSP_GMAC DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C1: GEL Output: --->>> EVE_VID_DSP DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C1: GEL Output: --->>> DSP DPLL already locked, now unlocking....

Cortex_M4_IPU1_C1: GEL Output: --->>> EVE_VID_DSP_DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C1: GEL Output: --->>> PRCM Clock Configuration for OPP 0 is DONE! <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> PRCM Configuration for all modules in progress... <<<---

Cortex_M4_IPU1_C1: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C1: GEL Output: module_offset: 0x000000C8

Cortex_M4_IPU1_C1: GEL Output: TIMEOUT

Cortex_M4_IPU1_C1: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C1: GEL Output: module_offset: 0x000000D0

Cortex_M4_IPU1_C1: GEL Output: TIMEOUT

Cortex_M4_IPU1_C1: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C1: GEL Output: module_offset: 0x000000D8

Cortex_M4_IPU1_C1: GEL Output: TIMEOUT

Cortex_M4_IPU1_C1: GEL Output: module_base: 0x4A009700

Cortex_M4_IPU1_C1: GEL Output: module_offset: 0x00000130

Cortex_M4_IPU1_C1: GEL Output: TIMEOUT

Cortex_M4_IPU1_C1: GEL Output: --->>> PRCM Configuration for all modules is DONE! <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> DDR3 initialization starts (TI 15x15 EVM)... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> DDR3 Initialization is in progress ... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> DDR DPLL clock config for 532MHz is in progress...

Cortex_M4_IPU1_C1: GEL Output: --->>> DDR DPLL already locked, now unlocking....

Cortex_M4_IPU1_C1: GEL Output: --->>> DDR DPLL clock config for 532MHz is in DONE!

Cortex_M4_IPU1_C1: GEL Output: Launch full leveling

Cortex_M4_IPU1_C1: GEL Output: Updating slave ratios in PHY_STATUSx registers

Cortex_M4_IPU1_C1: GEL Output: as per HW leveling output

Cortex_M4_IPU1_C1: GEL Output: HW leveling is now disabled. Using slave ratios from

Cortex_M4_IPU1_C1: GEL Output: PHY_STATUSx registers

Cortex_M4_IPU1_C1: GEL Output: --->>> DDR3 532MHz Initialization is DONE! <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Begin All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Begin All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Begin GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx End GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Begin GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx End GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx End All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx End All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Target Connect Sequence DONE !!!!! <<<---

Cortex_M4_IPU1_C1: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C1: GEL Output: For STM based tracing on TI EVMs,

Cortex_M4_IPU1_C1: GEL Output: run 'TDA3x EVM I2C EXPANDER CONTROL -> Enable_Trace_Pins()' function from Scripts menu on M4/CS_DAP_DebugSS

Cortex_M4_IPU1_C1: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C1: Can't Run Target CPU: (Error -1268 @ 0x1090001) Device is locked up in Hard Fault or in NMI. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.4.0.00129)。

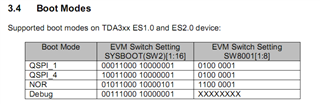

如下图所示,目前我16个开关引脚 SYSBOOT15-SYSBOOT0从高到低配置为00111000 10000001,另外一个SW8001我硬件上没画(Debug模式下不影响)。按照这种配置,理论上来时SYSBOOT7应该是1,但我看log里面是“Cortex_M4_IPU1_C1: GEL Output: --->>> 15x15 Package Detected(SYSBOOT[7]=0)... <<<---”,想咨询下是否是SYSBOOT的影响从而导致报错呢?(本设计中,SYSBOOT7并未连接到开关上,而是直接连的QSPI FLASH)

期待回复,万分感谢!