Hello Ti friends:

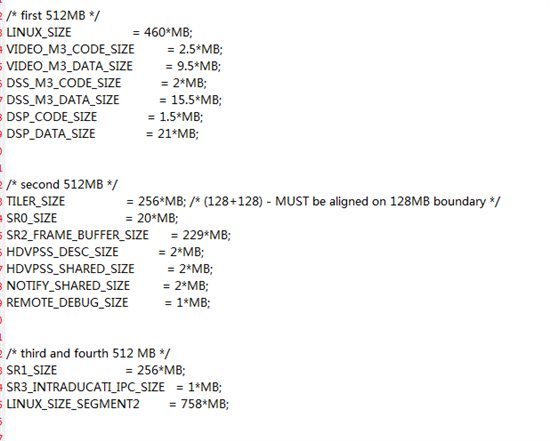

Here i meet a problem when i run load.sh. my config file is .

root@dvr:/opt/dvr_rdk/ti816x_2.8# ./load.sh

Attached to slave procId 2.

Loaded file ../firmware/dvr_rdk_fw_m3vpss.xem3 on slave procId 2.

Started slave procId 2.

After Ipc_loadcallback status [0x00000000]

After Ipc_startcallback status [0x097d2000]

[m3vpss ] ***** SYSTEM : Frequency <ORG> - 250000000, <NEW> - 280000000

[m3vpss ] notify_attach rtnVal 0

[m3vpss ] initProxyServer rtnVal 0

[m3vpss ]

[m3vpss ] *** UTILS: CPU KHz = 560000 Khz ***

[m3vpss ]

[m3vpss ] 43: SYSTEM : System Common Init in progress !!!

Attached to slave procId 1.

Loaded file ../firmware/dvr_rdk_fw_m3video.xem3 on slave procId 1.

Started slave procId 1.

After Ipc_loadcallback status [0x00000000]

After Ipc_startcallback status [0x00000000]

[m3video] ***** SYSTEM : Frequency <ORG> - 250000000, <NEW> - 280000000

[m3video]

[m3video] *** UTILS: CPU KHz = 560000 Khz ***

[m3video]

[m3video] 1355: SYSTEM : System Common Init in progress !!!

Attached to slave procId 0.

Loaded file ../firmware/dvr_rdk_fw_c6xdsp.xe674 on slave procId 0.

Started slave procId 0.

After Ipc_loadcallback status [0x00000000]

[c6xdsp ] ***** SYSTEM : Frequency <ORG> - 800000000, <NEW> - 800000000

[c6xdsp ]

[c6xdsp ] *** UTILS: CPU KHz = 800000 Khz ***

[c6xdsp ]

[c6xdsp ] 5: SYSTEM : System Common Init in progress !!!

After Ipc_startcallback status [0x00000000]

DMA: Module install successful, device major num = 250

DRV: Module install successful

DRV: Module built on Mar 22 2013 10:02:26

111

get bios_cat fail

[c6xdsp ] Remote Debug Shared Memory @ 0xbff00000

[m3video] Remote Debug Shared Memory @ 0xbff05020

[m3vpss ] Remote Debug Shared Memory @ 0xbff0a040

[c6xdsp ] 5634: MEM: Shared Region 2: Base = 0xb1400000, Length = 0x0e500000 (229 MB)

[m3video] 8052: MEM: Shared Region 2: Base = 0xb1400000, Length = 0x0e500000 (229 MB)

[m3vpss ] 8052: MEM: Shared Region 2: Base = 0xb1400000, Length = 0x0e500000 (229 MB)

[c6xdsp ] 5634: MEM: Shared Region 1: Base = 0xc0000000, Length = 0x10000000 (256 MB)

[m3video] 8052: MEM: Shared Region 1: Base = 0xc0000000, Length = 0x10000000 (256 MB)

[m3vpss ] 8052: MEM: Shared Region 1: Base = 0xc0000000, Length = 0x10000000 (256 MB)

[c6xdsp ] 5635: SYSTEM : System Common Init Done !!!

[m3video] 8054: SYSTEM : System Common Init Done !!!

[m3vpss ] 8054: SYSTEM : System Common Init Done !!!

[c6xdsp ] 5499: SYSTEM : System DSP Init in progress !!!

[m3video] 8054: SYSTEM : System Video Init in progress !!!

[m3vpss ] 8054: SYSTEM : System VPSS Init in progress !!!

[c6xdsp ] 5499: SYSTEM : RpeServer_init() done... Ret Val 0!!!

[m3video] 8054: SYSTEM : System Video Init Done !!!

[c6xdsp ] !!WARNING.Resource already registered:2

[c6xdsp ] 5507: SYSTEM : Initializing Links !!!

[m3vpss ] === HDVPSS Clocks are enabled ===

[m3vpss ] === HDVPSS is fully functional ===

[c6xdsp ] 5643: SYSTEM : FREE SPACE : System Heap = 10268448 B, Mbx = 10240 msgs)

[m3vpss ] === HDVPSS module is not in standby ===

[m3vpss ] === I2C1 Clk is active ===

[c6xdsp ] 5519: SYSTEM : Initializing Links ... DONE !!!

[c6xdsp ] 5519: SYSTEM : System DSP Init Done !!!

[m3video] 8081: HDVICP: Doing PRCM for IVAHD[0] ...

[m3vpss ] 8078: SYSTEM : HDVPSS Drivers Version: HDVPSS_01_00_01_37

[m3video] 8081: HDVICP: PRCM for IVAHD[0] ... DONE.

[m3vpss ] 8078: SYSTEM : FVID2 Init in progress !!!

[m3video] 8081: HDVICP: Doing PRCM for IVAHD[1] ...

[m3video] 8081: HDVICP: PRCM for IVAHD[1] ... DONE.

[m3video] 8081: HDVICP: Doing PRCM for IVAHD[2] ...

[m3video] 8081: HDVICP: PRCM for IVAHD[2] ... DONE.

[m3video] 8082: SYSTEM : Initializing Links !!!

[m3video] 8082: SYSTEM : FREE SPACE : System Heap = 6280232 B, Mbx = 0 msgs)

[m3video] 8083: SYSTEM : FREE SPACE : SR0 Heap = 18711424 B (17 MB)

[m3video] 8083: SYSTEM : FREE SPACE : Frame Buffer = 240123776 B (228 MB)

[m3video] 8083: SYSTEM : FREE SPACE : Bitstream Buffer = 268435328 B (255 MB)

[m3video] 8084: SYSTEM : FREE SPACE : Tiler Buffer = 0 B (0 MB) - TILER OFF

[m3vpss ] 8131: SYSTEM : FVID2 Init in progress DONE !!!

[m3vpss ] 8131: SYSTEM : Device Init in progress !!!

[m3video] 8107: SYSTEM : Initializing Links ... DONE !!!

[m3vpss ] initPrms.isI2cInitReq = 0

[m3vpss ] initPrms.isI2cInitReq = 0

[m3vpss ] 8134: SYSTEM : Device Init in progress DONE !!!

[m3vpss ] 8255: SYSTEM : System VPSS Init Done !!!

[m3vpss ] 8255: UTILS: DMA: HWI Create for INT62 !!!

[m3vpss ] 8255: SYSTEM : Initializing Links !!!

[m3vpss ] 8255: SYSTEM : FREE SPACE : System Heap = 13056 B, Mbx = -2 msgs)

[m3vpss ] 8255: SYSTEM : FREE SPACE : SR0 Heap = 18711424 B (17 MB)

[m3vpss ] 8256: SYSTEM : FREE SPACE : Frame Buffer = 235813760 B (224 MB)

[m3vpss ] 8256: SYSTEM : FREE SPACE : Bitstream Buffer = 268435328 B (255 MB)

it's pause forever.

who can help me? thanks for any help.