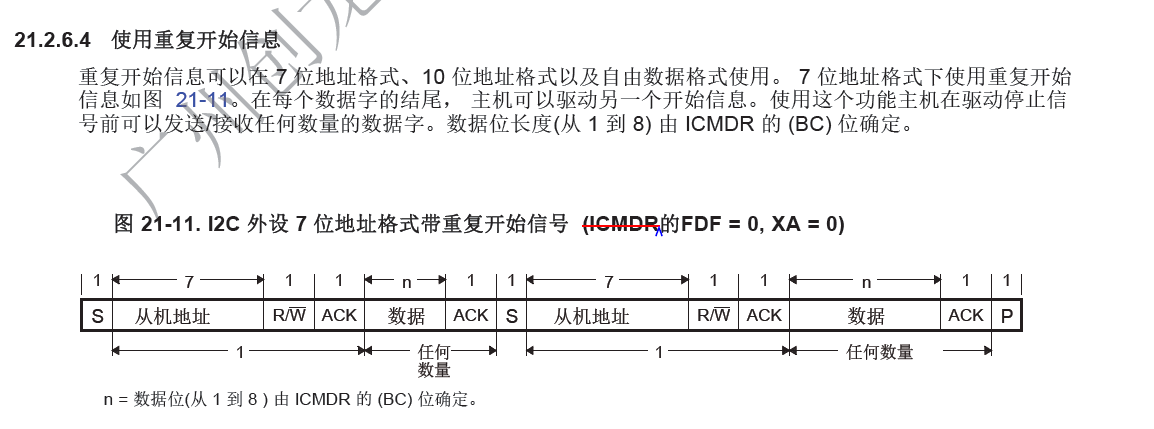

在使用6748中I2C的时候,怎么设置重复开始信息,如图所示

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

设置ICMDR寄存器的RM(Repeat Mode)位,具体请参考下面的TRM文档里的Table 21-14. I2C Mode Register (ICMDR) Field Descriptions (continued)。

https://www.ti.com/lit/ug/spruh79c/spruh79c.pdf

RM设置1是连续发送模式,但是上面表格中的协议是发送从机地址+从机寄存器地址后,在产生一个起始信号然后发送要读的地址的内容,第一阶段的从机地址+寄存器地址发送到第2个产生起始信号之间延时应该怎么确定,或者说产生第2个起始信号的时候,表明第一阶段的从机地址已经发送完毕了,那么怎么判断第一阶段的从机地址+寄存器地址发送完毕了,如果没有发送完毕,就产生第二个起始信号开始读操作,这个应该不对吧

抱歉看错了。

请看下面的配置。

A typical use case for a repeated start is doing a read from an EEPROM. In order to do so you would normally first do a write of the address from which you want to read, followed by a repeated start and then a read of that address. A repeated start can be accomplished by writing to the start bit (STT). The only "trick" is to set the bit at the correct time. The bit of interest in this case is the ARDY bit. You can either poll for this bit or get an interrupt. In either case, you should wait for ARDY before you re-program any of the I2C registers (e.g. switch from write to read and do the repeated start).

Here's an example that was written on DM355 (note this was not using Linux). It was to read a register from an AIC3204 data converter, so it is very similar to reading from an EEPROM. That is, first you write the address of the register and then perform a repeated start and then perform the read operation:

<syntaxhighlight lang='c'>

/* Check for Bus Busy */ while ((*I2C_ICSTR & ICSTR_BB));

/* Disable I2C during configuration */ *I2C_ICMDR = 0;

/* Set the I2C controller to write len bytes */ *I2C_ICCNT = write_len; *I2C_ICSAR = slaveaddr; *I2C_ICMDR = ICMDR_IRS | ICMDR_STT | ICMDR_TRX | ICMDR_MST | ICMDR_FREE;

/* Transmit data */

for (i = 0; i < write_len; i++)

{

// Wait for "XRDY" flag to transmit data or "ARDY" if we get NACKed while ( !(*I2C_ICSTR & (ICSTR_ICXRDY|ICSTR_ARDY)) );

// If a NACK occurred then SCL is held low and STP bit cleared if ( *I2C_ICSTR & ICSTR_NACK ) { *I2C_ICMDR = 0; // reset I2C so SCL isn't held low return RRET__FAIL; }

*I2C_ICDXR = write_data[i]; }

// wait for ARDY before beginning the read phase of the transaction while ( !(*I2C_ICSTR & ICSTR_ARDY) );

/* Set the I2C controller to read len bytes */ *I2C_ICCNT = read_len; *I2C_ICMDR = ICMDR_IRS | ICMDR_STT | ICMDR_STP | ICMDR_MST | ICMDR_FREE;

/* Receive data */

for (i = 0; i < read_len; i++)

{

// Wait for I2C to read data or or "ARDY" if we get NACKed

while( !(*I2C_ICSTR & (ICSTR_ICRRDY|ICSTR_ARDY)) ) {};

// If a NACK occurred then SCL is held low and STP bit cleared if ( *I2C_ICSTR & ICSTR_NACK ) { *I2C_ICMDR = 0; // reset I2C so SCL isn't held low return RRET__FAIL; }

// Make sure that you got the RRDY signal

while( !(*I2C_ICSTR & ICSTR_ICRRDY) ) {};

read_data[i] = *I2C_ICDRR;

}