- 我目前的配置:QSPI_CLOCK_CNTRL_REG 的 DCLK_DIV是0, CLKEN 是1

- 我的问题:

我从外部FLash的CLK引脚测试,测量只有12MHz。

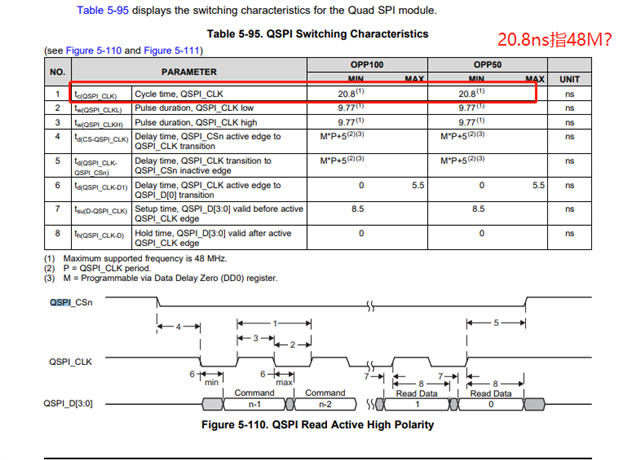

我是否可以通过更改程序设置,连接外部FLash之后,从外部FLash的CLK引脚测试,让时钟达到48MHz?

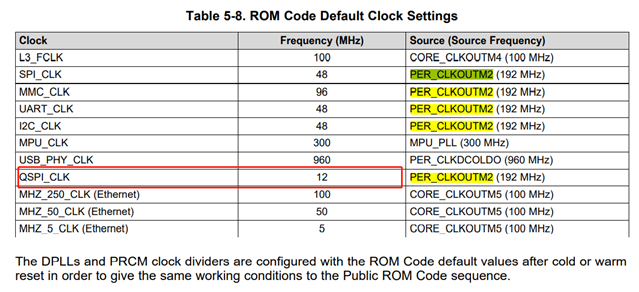

- 问题由来:ROM代码的QSPI_CLK默认默认设置为12MHz

,

,

https://www.ti.com/cn/lit/ds/symlink/am4379.pdf?ts=1654738324063 数据手册P231页表明QSPI_CLK最大支持频率为48MHz

。

。