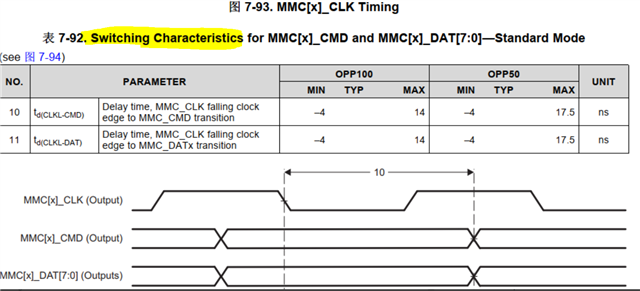

关于建立保持时间的设计问题,在AM335X规格书中看到部分总线接口有列出数据输出相对时钟延迟时间(例如下图),部分总线接口没有列举,

疑问:

(1)、该延迟时间对建立保持时间的影响,包括这个延迟时间范围误差很大,设计上如何考虑来满足建立保持时间;

(2)、为什么延迟时间误差范围很大;

(3)、为什么规格中有的总线没有延迟时间,以及没有延迟时间的话,如何满足建立保持时间的要求;

希望可以详细解答一下,想比较深入理解时序分析,谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

关于建立保持时间的设计问题,在AM335X规格书中看到部分总线接口有列出数据输出相对时钟延迟时间(例如下图),部分总线接口没有列举,

疑问:

(1)、该延迟时间对建立保持时间的影响,包括这个延迟时间范围误差很大,设计上如何考虑来满足建立保持时间;

(2)、为什么延迟时间误差范围很大;

(3)、为什么规格中有的总线没有延迟时间,以及没有延迟时间的话,如何满足建立保持时间的要求;

希望可以详细解答一下,想比较深入理解时序分析,谢谢!

该延迟时间对建立保持时间的影响,包括这个延迟时间范围误差很大,设计上如何考虑来满足建立保持时间;

这个图的参数是指信号的开关特性,即IO性能,是不可调节的。timing requirement才是时序要求。

(2)、为什么延迟时间误差范围很大;

大小是相对的,满足应用要求即可。

(3)、为什么规格中有的总线没有延迟时间,以及没有延迟时间的话,如何满足建立保持时间的要求;

具体指的哪个?

你好,下面三个问题回复如下,烦忙帮忙解答,谢谢

(1),我可以理解timming requirement是时序的要求,但是,我的疑问是,该延迟时间(io开关特性)会影响建立保持时间,范围误差这么大,怎么保证最坏情况下建立保持时间仍能满足外设要求(外设一般是标准件)

(2)不认同,按建立保持时间是相对平衡的,那这个延迟的最小值如何满足保持时间,最大值如何满足建立时间,设计上是怎么考虑的。

例如,外设为EMMC,AM3358往EMMC写数据(timing要求建立保持时间>3nS),按上图的误差时间套入,可以算一下余量,很小。

(3)反过来问,为什么有的总线设计的开关特性有延迟时间