1. TDA4VM PCIE时钟是否可以内部产生?还是一定需要外接时钟发生芯片?

如果可以自己内部产生,时钟是否可以通过PCIE_REFCLK管脚输出给外部PCIE设备?

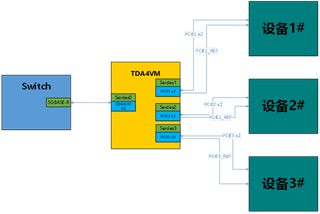

2. 如下是TDA4 PCIE连接的简图,帮忙确认一下是否有问题?

3. 如下图TDA4 Serdes0对接到Switch,TDA4采用QSGMII、Switch采用5GBASE-R,两者协议是否兼容?

4.提供一下TDA4VM支持的eMMC list.

5.确认一下TDA4VM pcie0 pcie1 pcie2的时钟内部是否同源?

6.TDA4VM MAIN RGMII 跑1000M速率是否一定要1.8V电平?3.3V电平是否支持1000M?