Part Number: TMS320C6655

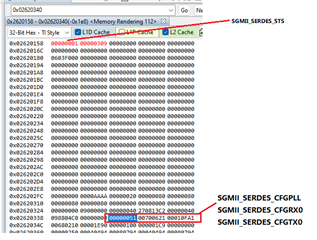

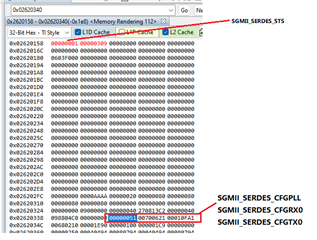

外接250MHz作为RapidIO/SGMII Reference Clock,通过配置寄存器SGMII_SERDES_CFGPLL,SGMII_SERDES_CFGRX0和SGMII_SERDES_CFGTX0(如图),之后查询SGMII_SERDES_STS寄存器,显示PLL锁定。

请教:该如何才能使得SerDes的PLL工作起来,输出1.25G的LinkRate。谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320C6655

外接250MHz作为RapidIO/SGMII Reference Clock,通过配置寄存器SGMII_SERDES_CFGPLL,SGMII_SERDES_CFGRX0和SGMII_SERDES_CFGTX0(如图),之后查询SGMII_SERDES_STS寄存器,显示PLL锁定。

请教:该如何才能使得SerDes的PLL工作起来,输出1.25G的LinkRate。谢谢!