Part Number: TMS320C6678

自制板

SRIO的4个lane两两组合分别连至两片FPGA芯片。在调试的时候设置为2x模式,分别与两片FPGA进行单独调试。现在DSP和第一片FPGA通过lane0-1可以link成功,而DSP和第二片FPGA通过lane2-3不能link成功。

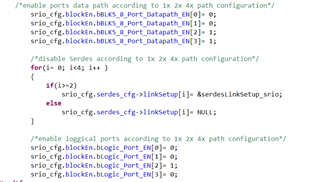

在调试第二片FPGA时,因为使用的是lane2-3,所以我在程序中做了如下修改 ,发现仍然link不通。

,发现仍然link不通。

请问上述的这种连接,SRIO支持吗?如果支持的话,那link不同可能是什么问题?程序中我还有什么没有修改对的地方?