1.GPIO口内部上下拉电阻阻值大概是多大的

2.当作为输入口使用时,关闭内部上下拉,外部一般需要多大的下拉电阻,可以保证低电平在0.8V以内

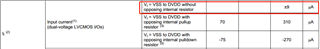

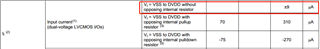

3.规格书P79页,±9uA电路如何理解,内部上拉时,电流在70-310uA变化的原因,通过该电流可以计算上下拉电阻吗

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

1.GPIO口内部上下拉电阻阻值大概是多大的

2.当作为输入口使用时,关闭内部上下拉,外部一般需要多大的下拉电阻,可以保证低电平在0.8V以内

3.规格书P79页,±9uA电路如何理解,内部上拉时,电流在70-310uA变化的原因,通过该电流可以计算上下拉电阻吗

1. 我这边没有具体的数值,但内部是弱上下拉的。

2. 外部电阻值的选取,请参考数据手册。

4.3 Pullup/Pulldown Resistors

https://www.ti.com/lit/ds/symlink/tms320c6748.pdf

3. 这是漏电流,在文档上有注释。上下拉电阻的阻值选择参考问题2的回复

II applies to input-only pins and bi-directional pins. For input-only pins, II indicates the input leakage current. For bi-directional pins, II indicates the input leakage current and off-state (Hi-Z) output leakage current.

作为输入口时,关闭内部上下拉,漏电流9uA.

打开内部上拉,漏电流70-310uA(忽略9uA), 是否可以推算出上拉电阻大概在10.6K-47K左右

打开内部下拉,漏电流75-270(忽略9uA),是否可以推算出下拉电阻大概在12.2K-44K左右