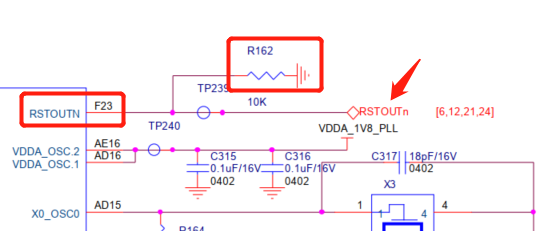

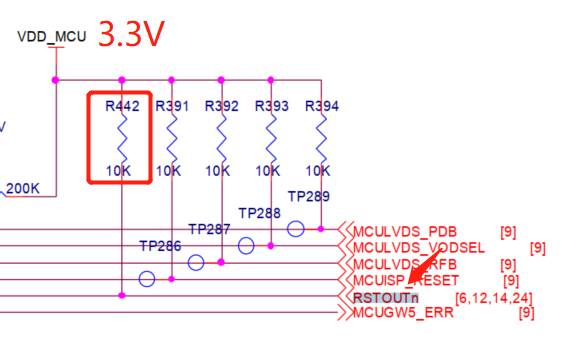

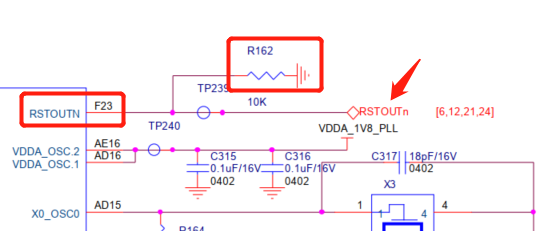

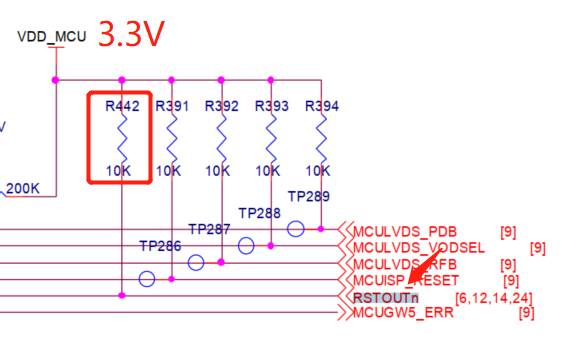

"RSTOUTN"(F23 PIN)脚在外部同时有上拉(3.3V)和下拉的情况下,测得该脚的电压仍为3.3V,不太能理解。请问这个PIN脚的内部电路是怎么样的?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

"RSTOUTN"(F23 PIN)脚在外部同时有上拉(3.3V)和下拉的情况下,测得该脚的电压仍为3.3V,不太能理解。请问这个PIN脚的内部电路是怎么样的?

该管脚内部有上下拉电阻,可通过软件配置。

具体可查看datasheet 表 4-2. Ball Characteristics 以及注释14. PULLUP / PULLDOWN TYPE

那内部配置为上拉的时候,即使外部加了下拉电阻,也不影响电平是吗?内部是通过什么结构上拉,PMOS强上拉吗?

该芯片我不是很熟悉,我需要咨询相关专家再给您回复,请问截图是来自于哪个文件?

截图的是我们自己的原理图,最初没有注意到设计上既有上拉,又有下拉,后来实际测量发现电平并没有变化,所以不太理解,麻烦帮忙咨询下相关专家,谢谢~

您好,

我们已将您的问题升级到英文论坛寻求帮助,链接如下,如有答复将尽快回复您:

您好,

RSTOUTn 是一个被驱动的输出(非开漏)。 如处理器data manual中所描述的,RSTOUTn 仅会在 VDDSHV3有效后才有效。 如果 RSTOUTn 信号被用作其它器件的复位信号,必须与 PORz 搭配使用以防止在功率斜升期间出现毛刺脉冲。 下拉电阻有助于在功率斜升期间保持信号低电平,但还是建议使用带有PORz 输入的AND'd。

Hi, Cherry

谢谢您的回复!

RSTOUTn要和PORz搭配使用作为复位信号,这点已经理解了,谢谢。

但是,“被驱动的输出”和“开漏输出”在电路结构上有什么区别?“被驱动的输出”电路指的是“推挽电路”吗?

是否推挽电路的输出在上拉或下拉时电平是不受影响的?

您好,

被驱动的输出”电路指的是“推挽电路”吗?

是的。

是否推挽电路的输出在上拉或下拉时电平是不受影响的?

是的,下拉仅在器件上电或断电期间有影响。