各位工程师,你们好:

我们在调试TMS320C6678芯片与V7(FPGA)的TSIP接口时,遇到了如下问题:

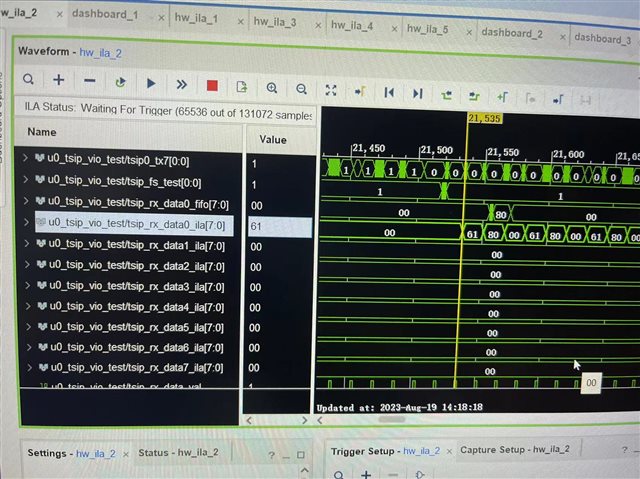

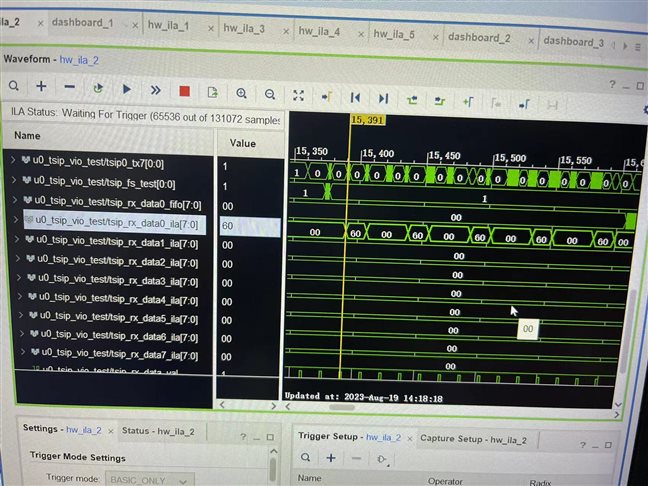

1.TMS320C6678通过TSIP发送给FPGA的数据不是按照手册描述的八位数据紧接着八位数据,而是24b一个数据,如下图所示,总结目前看到的数据规律为:8b数据+16b空闲码。这个问题严重影响了我的传输带宽。

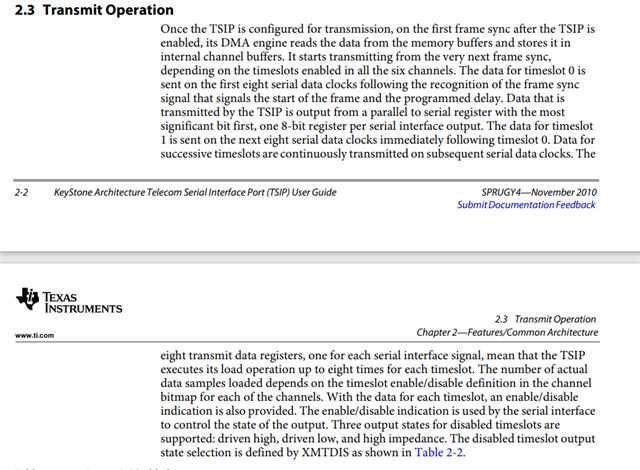

手册描述:

实际现象:

2.TMS320C6678通过TSIP发送给FPGA的数据会丢掉前边的一部分数据,丢包长度还不固定,后边数据经过检验都是正确的,我们发现TI官方程序内部的检验逻辑不关注前边数据是否丢失,但是这个情况将影响我们实际使用时命令的收发。

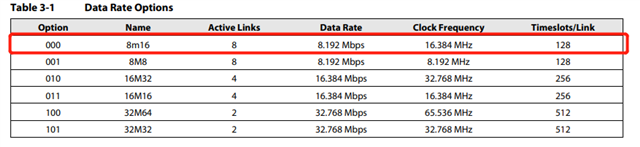

目前使用的TMS320C6678驱动为TI官方提供的:ccs930/pdk_c667x_2_0_16,工作模式如下:

任意的帮助都将不胜感激,期待您的回复,谢谢!