Part Number: AM3352

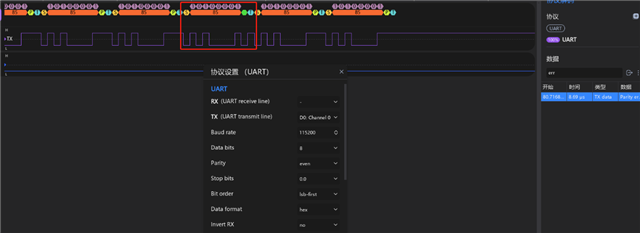

After testing, it has been found that the serial port of the AM335x chip has a higher probability of encountering parity errors. In the manual, a baud rate of 115200 is recommended. By capturing data with a logic analyzer for statistical analysis, it was observed that the probability of parity errors is 0.00083%. In the same test environment, the ST chip did not encounter any parity errors. In order to eliminate the interference from peripheral circuits, I directly connected the TX and GND of the chip's IO port to the logic analyzer. The test results were consistent with the previous findings, indicating that it is not related to the peripheral circuits.

Since most high baud rate configurations are not within the range specified in the manual, there is a significant discrepancy between the actual baud rate and the configured one. However, by directly analyzing the data using a logic analyzer, the actual baud rate can be determined for decoding. In the tests, it was found that configuring odd or even parity had no impact on the experimental results, so a configuration of 8 data bits, 1 stop bit, and even parity was used. The test data is as follows:

|

Baud Rate |

Mode (Data bits-Stop bits-Parity) |

Number of transmitted bytes |

Number of parity bit errors |

Error rate |

|

576000 |

8-1-e |

5120 |

127 |

2.4805% |

|

512000 |

8-1-e |

5120 |

125 |

2.4414% |

|

384000 |

8-1-e |

5120 |

93 |

1.8164% |

|

288000 |

8-1-e |

5120 |

128 |

2.5% |

|

256000 |

8-1-e |

5120 |

9 |

0.1758% |

|

192000 |

8-1-e |

5120 |

1 |

0.01953% |

|

115200 |

8-1-e |

480000 |

1 |

0.000208% |

|

57600 |

8-1-e |

4800000 |

0 |

0% |

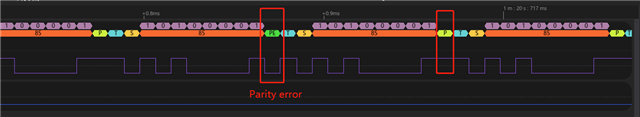

The figure below shows occasional parity bit errors that occurred at a baud rate of 115200.

Configuration details: The serial port configuration clock adopts the default 48M as specified in the manual.

I hope to receive a practical solution to this issue.