Part Number: TDA4VH-Q1

Other Parts Discussed in Thread: TDA4VM

需要tda4vh-sdk8.6中输出refclk 100Mhz

采用以上patch在vh中无效

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

已咨询e2e工程师,请看下面的回复。

I see that TDA4VH is the SoC in use. Could you try below patch for using internal refclk?

enable_internal_ref_clock_out_pcie1_j784s4.patch

TDA4VH-Q1: tda4vh-pcie refclk - Processors forum - Processors - TI E2E support forums

--- a/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

+++ b/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@ -729,7 +729,7 @@ &serdes1 {

status = "okay";

serdes1_pcie_link: phy@0 {

reg = <0>;

- cdns,num-lanes = <2>;

+ cdns,num-lanes = <4>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>;

@@ -745,11 +745,14 @@ &pcie0_rc {

reset-gpios = <&exp1 6 GPIO_ACTIVE_HIGH>;

phys = <&serdes1_pcie_link>;

phy-names = "pcie-phy";

+ status = "okay";

+

};

&pcie0_ep {

phys = <&serdes1_pcie_link>;

phy-names = "pcie-phy";

+ status = "disabled";

};

&pcie1_rc {

@@ -783,7 +786,8 @@ &serdes_ln_ctrl {

<J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>, <J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>, <J784S4_SERDES1_LANE3_PCIE0_LANE3>,

- <J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>;

+ <J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>,

+ <J784S4_SERDES2_LANE2_IP3_UNUSED>,<J784S4_SERDES2_LANE2_IP4_UNUSED>;

};

&main_udmass_inta {

diff --git a/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c b/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

index f04619634..34b44c31f 100644

--- a/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

+++ b/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

@@ -2780,6 +2780,27 @@ static int cdns_torrent_phy_probe(struct platform_device *pdev)

if (ret)

goto put_lnk_rst;

}

+ /* Un-lock Partition 7 : 8000h to 9FFFh */

+ writel(0x68EF3490, ioremap(0x011D008, 0x4)); /* LOCK7_KICK0 */

+ writel(0xD172BC5A, ioremap(0x011D00C, 0x4)); /* LOCK7_KICK1 */

+ /* Un-lock Partition 1 : 4000h to 5FFFh */

+ writel(0x68EF3490, ioremap(0x00105008, 0x4)); /* LOCK1_KICK0 */

+ writel(0xD172BC5A, ioremap(0x0010500C, 0x4)); /* LOCK1_KICK1 */

+

+ /* Un-lock Partition 2 : 8000h to 9FFFh */

+ writel(0x68EF3490, ioremap(0x00109008, 0x4)); /* LOCK2_KICK0 */

+ writel(0xD172BC5A, ioremap(0x0010900C, 0x4)); /* LOCK2_KICK1 */

+

+

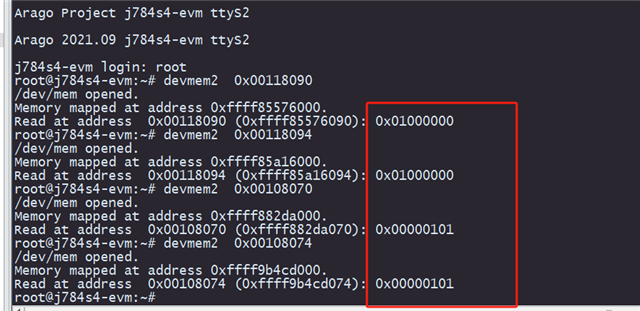

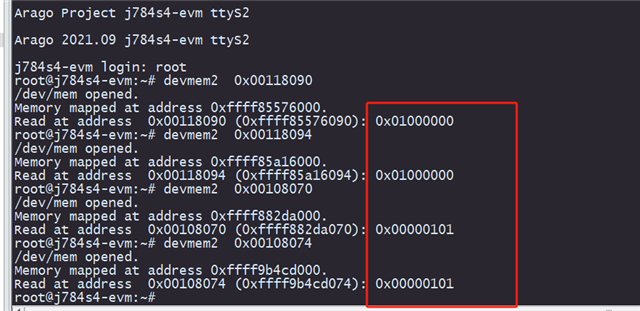

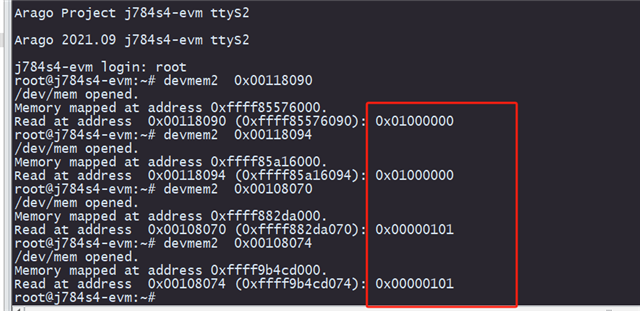

+ /* Enable ACSPCIe0 PAD 0 and 1 */

+ writel(0x01000000, ioremap(0x00118090, 0x4));

+ /* Enable ACSPCIe1 PAD 0 and 1 */

+ writel(0x01000000, ioremap(0x00118094, 0x4));

+

+ /* PCIE_REFCLK0_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel(0x00000101, ioremap(0x00108070, 0x4));

+ /* PCIE_REFCLK1_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel(0x00000101, ioremap(0x00108074, 0x4));

diff --git a/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts b/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

index 492975144..8a3f17450 100644

--- a/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

+++ b/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@ -729,7 +729,7 @@ &serdes1 {

status = "okay";

serdes1_pcie_link: phy@0 {

reg = <0>;

- cdns,num-lanes = <2>;

+ cdns,num-lanes = <4>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>;

@@ -745,11 +745,14 @@ &pcie0_rc {

reset-gpios = <&exp1 6 GPIO_ACTIVE_HIGH>;

phys = <&serdes1_pcie_link>;

phy-names = "pcie-phy";

+ status = "okay";

+

};

&pcie0_ep {

phys = <&serdes1_pcie_link>;

phy-names = "pcie-phy";

+ status = "disabled";

};

&pcie1_rc {

@@ -783,7 +786,8 @@ &serdes_ln_ctrl {

<J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>, <J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>, <J784S4_SERDES1_LANE3_PCIE0_LANE3>,

- <J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>;

+ <J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>,

+ <J784S4_SERDES2_LANE2_IP3_UNUSED>,<J784S4_SERDES2_LANE2_IP4_UNUSED>;

};

&main_udmass_inta {

diff --git a/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c b/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

index f04619634..34b44c31f 100644

--- a/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

+++ b/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

@@ -2780,6 +2780,27 @@ static int cdns_torrent_phy_probe(struct platform_device *pdev)

if (ret)

goto put_lnk_rst;

}

+ /* Un-lock Partition 7 : 8000h to 9FFFh */

+ writel(0x68EF3490, ioremap(0x011D008, 0x4)); /* LOCK7_KICK0 */

+ writel(0xD172BC5A, ioremap(0x011D00C, 0x4)); /* LOCK7_KICK1 */

+ /* Un-lock Partition 1 : 4000h to 5FFFh */

+ writel(0x68EF3490, ioremap(0x00105008, 0x4)); /* LOCK1_KICK0 */

+ writel(0xD172BC5A, ioremap(0x0010500C, 0x4)); /* LOCK1_KICK1 */

+

+ /* Un-lock Partition 2 : 8000h to 9FFFh */

+ writel(0x68EF3490, ioremap(0x00109008, 0x4)); /* LOCK2_KICK0 */

+ writel(0xD172BC5A, ioremap(0x0010900C, 0x4)); /* LOCK2_KICK1 */

+

+

+ /* Enable ACSPCIe0 PAD 0 and 1 */

+ writel(0x01000000, ioremap(0x00118090, 0x4));

+ /* Enable ACSPCIe1 PAD 0 and 1 */

+ writel(0x01000000, ioremap(0x00118094, 0x4));

+

+ /* PCIE_REFCLK0_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel(0x00000101, ioremap(0x00108070, 0x4));

+ /* PCIE_REFCLK1_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel(0x00000101, ioremap(0x00108074, 0x4));

phy_provider = devm_of_phy_provider_register(dev, of_phy_simple_xlate);

if (IS_ERR(phy_provider)) {

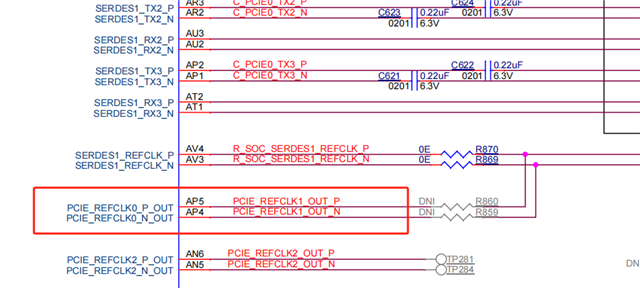

测量R860 R859一侧,电平幅度由0V变成1.8V,频率不断变动,不在100mhz附近

note:用的是贵司的VH开发板

R860 R859在pcb上没有贴电阻,是的,频率不对,波形看起来是波动的噪声

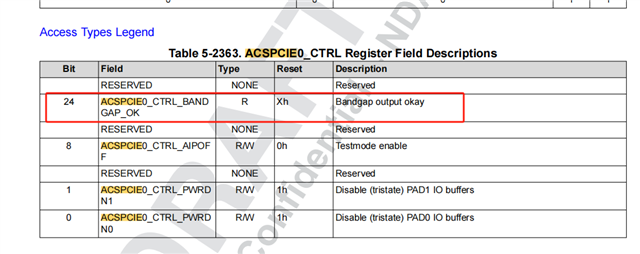

信号幅度变化是因为将bit24置1了,测试了一下,证实 是,如果置1是1.8v,置0是0v

/* PCIE_REFCLK0_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */ writel(0x00000101, ioremap(0x00108070, 0x4)); /* PCIE_REFCLK1_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */ writel(0x00000101, ioremap(0x00108074, 0x4));

PCIE_REFCLK1_P_OUT应该与serdes无关?只是由系统输出?

请看下面e2e工程师的回复。

What the patch should do is route the internal clock to the refclk for SERDES configured for PCIe. I will need some time to take a look at it. It looks like some registers are correct since the voltage level is changing, but not all are correct since it looks like noise instead of actual clock.

Patch for SDK7.3:

Patch for SDK8.x:

中

regmap_field_write(cdns_phy->phy_pma_cmn_ctrl_rcv_out_en, 0x3); regmap_field_write(cdns_phy->cmn_plllc_clk1_en, 0x1); regmap_field_write(cdns_phy->cmn_plllc_clk1outdiv, 0x2e);

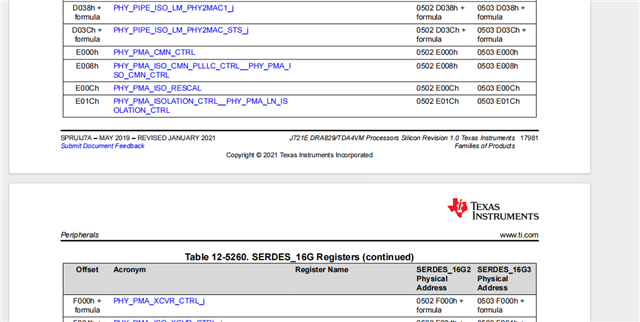

按代码中寄存器有offset应该是e09a,但寄存器中没有说,是否是没有公开出来

请看下面e2e工程师的回复。

Some of the registers might not be in the TRM, because the registers are taken from some IP documentation directly from Cadence.

Although, the patches you are referencing are for the TDA4VM which has a different SERDES called the sierra, whereas TDA4VH has the torrent SERDES, so SERDES register offsets would be different between the two. To clarify, is the device being used the TDA4VH or the TDA4VM?