Part Number: TDA4VM

您好,

我想在A72运行linux的同时也在mcu1_0上启动运行SDK中mcusw->mcal_drv->examples->Can的提供的示例代码,我看官方提供了spl的方式8.3.MCU1_0 使用 SYSFW 进行应用程序开发 — 处理器 SDK RTOS J721E,但是我按照文档操作后仍然无法启动,我不知道mcal_drv的例子是需要增加SYSFW固件启动么? 可以为我修改提供帮助么

1.我在makefile中,修改DM的路径

2.我make u-boot 后替换了sysfw.itb tiboot3.bin tispl.bin u-boot.img文件到boot

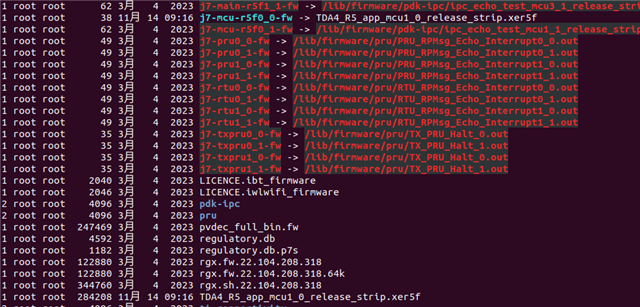

3.我修改了软连接如下 j7-mcu-r5f0_0-fw -> TDA4_R5_app_mcu1_0_release_strip.xer5f

但系统无法启动,日志如下

U-Boot SPL 2021.01 (Nov 14 2023 - 09:20:40 +0800)

Model: Texas Instruments J721E SK R5

Board: J721EX-EAIK rev A1

SYSFW ABI: 3.1 (firmware rev 0x0008 '8.6.3--v08.06.03 (Chill Capybar')

Trying to boot from MMC2

Starting ATF on ARM64 core...

NOTICE: BL31: v2.8(release):v2.8-226-g2fcd408bb3-dirty

NOTICE: BL31: Built : 22:56:45, Mar 3 2023

I/TC:

I/TC: OP-TEE version: 3.20.0 (gcc version 9.2.1 20191025 (GNU Toolchain for the A-profile Architecture 9.2-2019.12 (arm-9.10))) #1 Fri Mar 3 22:59:24 UTC 2023 aarch64

I/TC: WARNING: This OP-TEE configuration might be insecure!

I/TC: WARNING: Please check https://optee.readthedocs.io/en/latest/architecture/porting_guidelines.html

I/TC: Primary CPU initializing

I/TC: SYSFW ABI: 3.1 (firmware rev 0x0008 '8.6.3--v08.06.03 (Chill Capybar')

I/TC: HUK Initialized

E/TC:0 0 k3_sec_proxy_verify_thread:108 Queue is busy

E/TC:0 0 k3_sec_proxy_recv:196 Thread SEC_PROXY_RESPONSE_THREAD verification failed. ret = -65523

E/TC:0 0 ti_sci_get_response:101 Message receive failed (-65523)

E/TC:0 0 ti_sci_do_xfer:150 Failed to get response (-65523)

E/TC:0 0 sa2ul_init:59 Failed to get SA2UL device

E/TC:0 0 call_initcalls:43 Initcall __text_start + 0x00063c20 failed

I/TC: Primary CPU switching to normal world boot

E/TC:0 0

E/TC:0 0 Core data-abort at address 0x10 (translation fault)

E/TC:0 0 esr 0x96000005 ttbr0 0x9e894000 ttbr1 0x00000000 cidr 0x0

E/TC:0 0 cpu #0 cpsr 0x800003c4

E/TC:0 0 x0 000000009e867000 x1 0000000000000010

E/TC:0 0 x2 0000000000000000 x3 0000000000000000

E/TC:0 0 x4 0000000000000001 x5 0000000000ffffff

E/TC:0 0 x6 0000000000000002 x7 000000009e89c190

E/TC:0 0 x8 000000009e89c190 x9 000000009e884d70

E/TC:0 0 x10 0000000000000000 x11 0000000000000000

E/TC:0 0 x12 000000009e89c100 x13 000000000000000a

E/TC:0 0 x14 00000000ffffffff x15 0000000000000020

E/TC:0 0 x16 000000009e813c40 x17 0000000000000000

E/TC:0 0 x18 0000000000000000 x19 000000009e89eca0

E/TC:0 0 x20 000000009e89eca8 x21 0000000000000007

E/TC:0 0 x22 000000009e873000 x23 000000009e8736a0

E/TC:0 0 x24 0000000100000000 x25 0000000000000000

E/TC:0 0 x26 0000000000000000 x27 0000000000000000

E/TC:0 0 x28 0000000000000000 x29 000000009e89ec30

E/TC:0 0 x30 000000009e80e3ac elr 000000009e80e3cc

E/TC:0 0 sp_el0 000000009e89ec30

E/TC:0 0 TEE load address @ 0x9e800000

E/TC:0 0 Call stack:

E/TC:0 0 0x9e80e3cc

E/TC:0 0 Panic 'unhandled pageable abort' at core/arch/arm/kernel/abort.c:572 <abort_handler>

E/TC:0 0 TEE load address @ 0x9e800000

E/TC:0 0 Call stack:

E/TC:0 0 0x9e8087dc

E/TC:0 0 0x9e81506c

E/TC:0 0 0x9e807fd8

E/TC:0 0 0x9e805520