Part Number: TMS320C6657

1.开发环境

CCS版本号:V5.5.0.0007

PDK版本号:1.1.2.6

2.例程需求描述

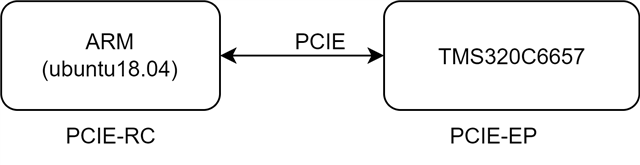

2.1 设计框图如下:

(1)ARM端作为PCIE-RC设备,运行的是Ubuntu18.04系统;

(2)TMS320C6657作为PCIE-EP设备,运行的固件是“D:\ti\pdk_C6657_1_1_2_6\packages\ti\drv\exampleProjects\PCIE_exampleProject”的PCIE_exampleProject

3.问题及需求描述

问题:在PCIE_exampleProject例程中,PCIE BAR的配置只是映射了L2 SRAM的地址,如何将DDR3的地址映射到PCIE域进行数据读写测试,

需求:

(1)如何配置PCIE的参数及地址,完成DDR3的地址映射?是否有参考代码?

(2)完成参数及地址配置后,如何向DDR3内存地址中写入数据,便于RC端读取?如何读取DDR3内存地址中的数据,来确认RC端已经向PCIE EP写入数据?是否有参考代码?

(3)如不能在PCIE_exampleProject例程进行修改完成需求,那是否有其他PCIE数据通信和读写速率的例程可以参考?