Part Number: TMS320C6678

Other Parts Discussed in Thread: TPIC2060A

The SPI has the following features:

Up to 66 MHz operation

上面关于《Serial Peripheral Interface( SPI) for KeyStone Devices User'sGuide》说明书提到最高支持66 MHZ 的操作。

在C6678的硬件平台下,在3.3us(3300ns)中断周期内实施SPI的二路总线控制,进行多次SPI读写数据(DSP向TPIC2060A(35M=28.6ns)、AD・DA(48M=21ns)板使用SPI进行数据传输)。其中36M SPI 器件一个读写寄存器都是16(数据位)+2(启动)*28.6ns=514.8ns。

遇到问题,理论计算中断周期内3300/515=6.4可以进行SPI通讯次数6.4。但是实际发送时,只发送4次就中断周期超时了2.3us(5.6us),3个超时1us(4.3),估算5.6-4.3=1.3us,一次发送使用时间为1.3us,远远超过了514.8ns。

SPI 通讯参考了TI的《7242.K1_STK_v1.1》SPI驱动代码:

//参考案例中,SPI通讯采用是读写同步方法(边写边读方式)函数名如下:

Uint32 KeyStone_SPI_TxRx(Uint8 * txBuf, Uint32 firstTxByte,

Uint32 numTxByte, Uint8 * rxBuf, Uint32 firstRxByte, Uint32 numRxByte,

SPI_Transfer_Param * transfer)

检查程序中,发现上面函数调用了KeyStone_SPI_wait_flag函数延时检查TXINTFLG和RXINTFLG状态。

代码:if(0==KeyStone_SPI_wait_flag(CSL_SPI_SPIFLG_RXINTFLG_MASK, CSL_SPI_SPIFLG_RXINTFLG_MASK))

#define SPI_TIMEOUT_CYCLES ((1000)*8*100)

Int32 KeyStone_SPI_wait_flag(Uint32 flag_mask, Uint32 expect)

{

Uint32 startTSC;

Uint32 delay;

volatile Uint32 flag;

startTSC= TSCL;

//flag_mask:CSL_SPI_SPIFLG_RXINTFLG_MASK

flag= gpSPI_regs->SPIFLG&flag_mask; //CSL_SPI_SPIFLG_RXINTFLG_MASK (0x00000100u)

/*Wait until SPI flag= expect value */

//1 = Transmit buffer is empty. An interrupt is pending to fill the transmitter.

while(flag!= expect)

{

/*if wait time is much larger than theoretical transfer time of

a byte, then it is looked as timeout.*/

delay= TSC_getDelay(startTSC);

// printf("KeyStone_SPI_wait_flag delay= %d \n",delay);

if(delay> SPI_TIMEOUT_CYCLES)

{

printf("KeyStone_SPI_wait_flag 0x%x timeout, SPIFLG=0x%x\n",

flag_mask, gpSPI_regs->SPIFLG);

return 0;

}

flag= gpSPI_regs->SPIFLG&flag_mask;

};

return 1;

}

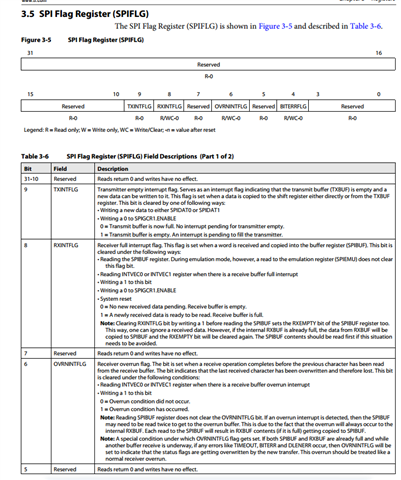

函数的作用是判断SPI Flag Register (SPIFLG)中TXINTFLG和RXINTFLG,其中有延时等待代码判断TXINTFLG和RXINTFLG是否为1,产生延时。

起初,尝试修改#define SPI_TIMEOUT_CYCLES ((1000)*8*100)---〉#define SPI_TIMEOUT_CYCLES ((400)*1*1),运行SPI传输时间没有发生变化。

再在 KeyStone_SPI_TxRx函数中屏蔽了写入TXINTFLG判断,4次SPI通讯中断周期变成4.7us(比过去5.6us短0.9us)。此时,两个SPI控制IC读取写寄存器数据OK。

最后,在KeyStone_SPI_TxRx函数中屏蔽了写入RXINTFLG判断,中断周期恢复到正常的3.3us。但是两个SPI控制IC读取寄存器数据NG,但是写入数据ic动作了。

1、SPI 说明书中最大操作速度66MHZ,指的是SPIDAT1或SPIBUF寄存器数据转换速度也能支持到66MHZ。

2、为了保证SPI传输数据正确性,读写SPIDAT1或SPIBUF寄存器前都需要判断TXINTFLG和RXINTFLG标志位吗?从说明书理解写入新的SPIDAT1数据时,TXINTFLG会更新,那么写入数据时候需要判断吗?

3、现在屏蔽了写入RXINTFLG判断,中断周期恢复到正常的3.3us,并且IC有动作(感觉动作正常),能说明被控IC读取到SPI的发送数据,能排除硬件电路问题吗?