你好,

SDK:https://www.ti.com.cn/tool/cn/download/PROCESSOR-SDK-LINUX-RT-AM57X/06.00.00.07

开发板:https://www.ti.com.cn/tool/cn/TMDSIDK574?keyMatch=TMDSIDK5748

我现在在使用igh-ethercat1.5主站程序来进行主站从站之间的通讯。主站是ti的am5748,从站是倍福的模拟输入输出IO模块。我是基于官方提供的sdk linux-rt 06.00.00.07内核编译的igh主站程序,在编译完成后在linux环境中进行输入输出的延时测试。对延时测试的思想如下:信号发生器给模拟输入通道一个波形,让模拟输出通道输出相同的波形。将两个通道接在示波器上测试输入输出的延时。

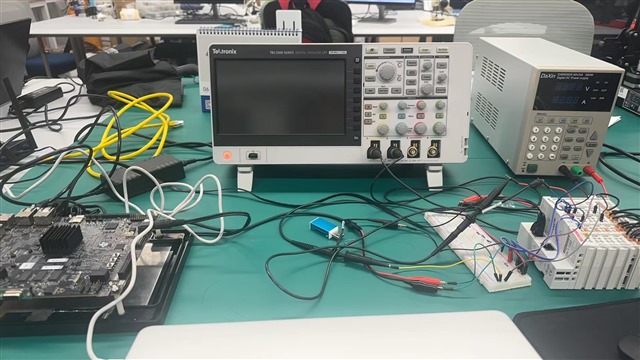

搭建的系统如下所示:

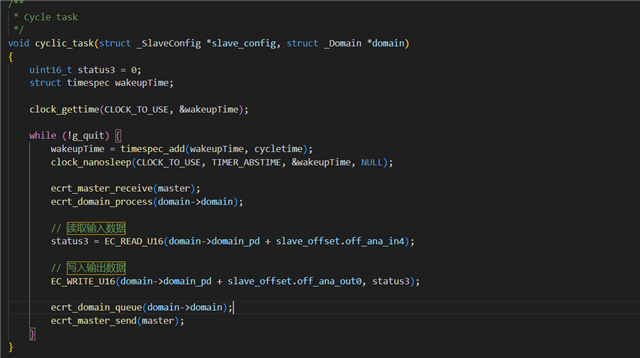

对输入输出数据的处理代码如下(若需全部代码请告知):

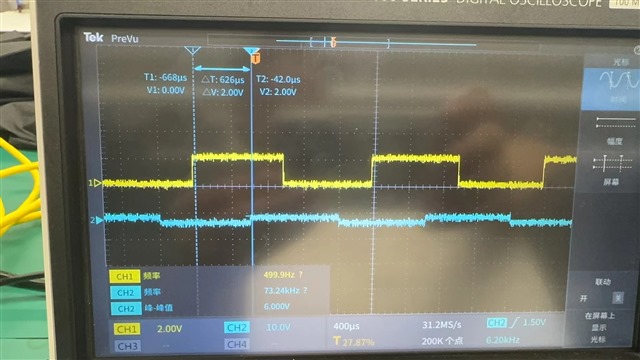

测到的延时如下所示:

可从图中看到延时高达626微秒。

我想知道这么大的延时改怎么解决?请提供一些解决思路