Part Number: TMS320C6748

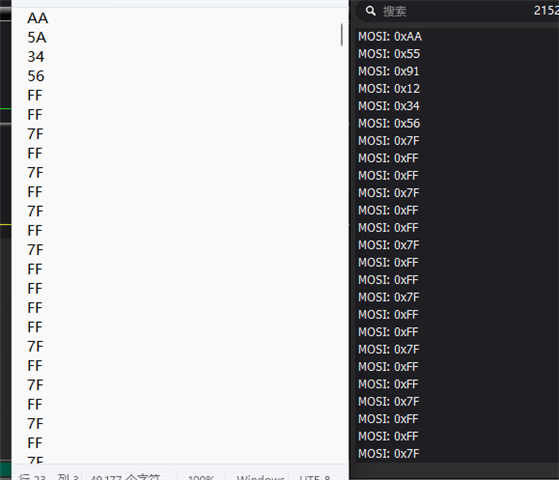

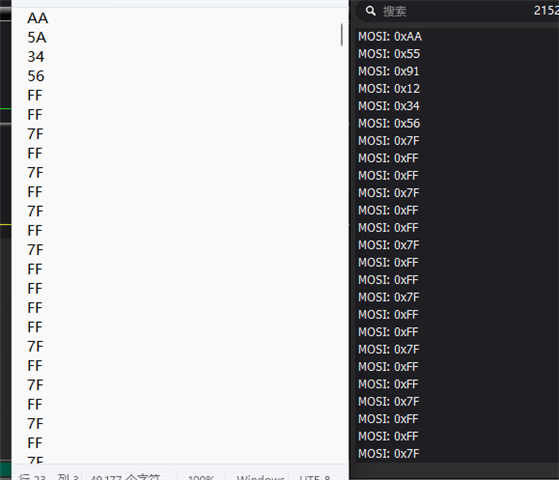

我用FPGA对C6748通过SPI发送数据,我对比了用逻辑分析仪获取到的主机发送的数据,并与从机接收到的数据进行了对比,发现接收到的数据存在部分缺失。请问我应该如何解决?下图左侧为从机接收到的数据,右侧为逻辑分析仪抓取到的主机发出的数据

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320C6748

我用FPGA对C6748通过SPI发送数据,我对比了用逻辑分析仪获取到的主机发送的数据,并与从机接收到的数据进行了对比,发现接收到的数据存在部分缺失。请问我应该如何解决?下图左侧为从机接收到的数据,右侧为逻辑分析仪抓取到的主机发出的数据

您好,

请参考开发指南“6.8. McSPI-QSPI-OSPI”,测试其CCS例程。

6.1. CSL — Processor SDK RTOS Documentation

也可参考这个帖子中分享的例程