Part Number: AM6442

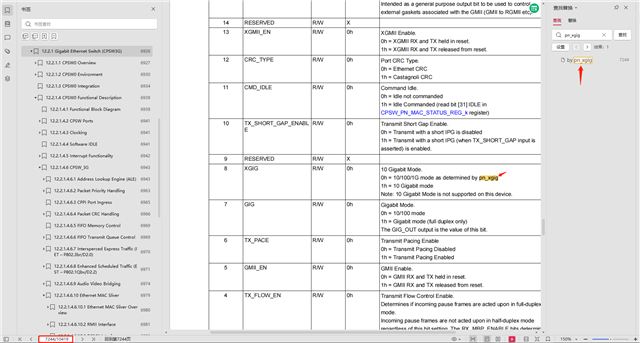

CPSW_PN_MAC_CONTROL_REG_k Register bit[8]XGIG 表明 MAC传输速度取决于 pn_xgig; TRM检索不到pn_xgig的相关说明? 如何令RMII工作于100 mode?(目前10 mode工作正常,100 mode 找不到设置方法)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AM6442

CPSW_PN_MAC_CONTROL_REG_k Register bit[8]XGIG 表明 MAC传输速度取决于 pn_xgig; TRM检索不到pn_xgig的相关说明? 如何令RMII工作于100 mode?(目前10 mode工作正常,100 mode 找不到设置方法)

您好

我们看了您发的几个帖子并为您做了进一步咨询,请等待资深工程师在下方帖子中的回复。

I was on vacation. So could not check on this.

Will get back to you by next week.

帖子回复我已经查看。

麻烦帮我转述一下:

①板子是自己定制的,使用的是AM6442芯片型号;采用的RMII引脚组合在上方帖子有提及。

②在贵司的AM64X-EVM板子中已经完成CPSW RGMII开发,关于CPSW相关驱动几乎全部采用的寄存器方式开发,且已经进行充分的测试验证。这足以表明独立进行的寄存器开发,是有这个开发能力的。 然后在自己定制的板子中。我将相应的寄存器配置修改为RMII方式。发现关于RMII寄存器的描述很少,甚至存在错误(上方帖子有提及)。

③涉及保密因素,我无法提供寄存器配置给到您。但是我相信TRM关于CPSW的RMII相关寄存器描述是缺失或者错误的。比如上方帖子提及的寄存器0x08022330。

我希望您能充分阅读上方帖子,并解答相应疑问。

④我通过如下方式,已经确定端口选用的是RMII接口。

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, 1);

*(vuint32_t*)(0x43004044) = 1; //cpsw0-port1 2选择RGMII 1选择RMII

*(vuint32_t*)(0x43004048) = 1; //cpsw0-port2 2选择RGMII 1选择RMII

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, 1);

⑤在SDK C:\ti\mcu_plus_sdk_am64x_09_02_00_50\examples\networking\enet_layer2_cpsw 例程中,我尝试将这个示例修改为RMII接口,但是很遗憾,它甚至连10M模式都无法工作。

贵司是否充分验证过RMII接口?能否提供CPSW 的RMII接口例程。如能提供,我想我应该可以独立解决RMII只工作于10M,而无法进行100M通信的问题。

好的。帖子已经查看。能否请您将 关于RMII寄存器描述缺失的问题反应到TRM的相关工作人员?(具体缺失和错误在我发布的帖子有提到)

然后麻烦帮我转述一下:

①定制板我和同事说下,让他和贵司FAE进行 硬件板子的问题检查。

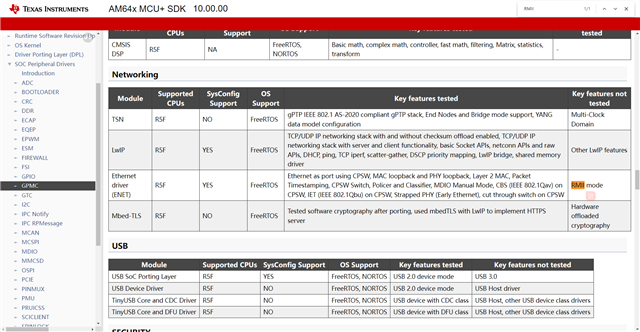

②例程并不是最新的,但是从文件索引能看出SDK版本,该版本的SDK足够新。自我开发AM6442开始,在贵司官网已下载了不下于4个SDK版本。 刚去看了最新的SDK发布说明,RMII并未进行测试验证 ,因此不想继续更新SDK版本进行测试了。

③PHY同样的电路和软件配置在其余项目中使用是正常的。

其次,从AM6442 的RMII_TD0 RMII_TD1 RMII_TEN信号,通过示波器抓取波形,显示工作于10M的工作频率,我无法令它工作于100M.

最后,我尝试将PHY 配置为 10M模式,数据收发是正确无误的。这表明我对CPSW RMII的配置应该不存在过多的纰漏 。

唯一问题就是为何令PHY配置为100M模式,CPSW 的 RMII接口模式为何不自动调整为100M? 既然无法自动调整,为何不提供修改RMII接口时序的寄存器配置? 我想这应该足以表明10M问题的来源 并不是来自 PHY的配置。

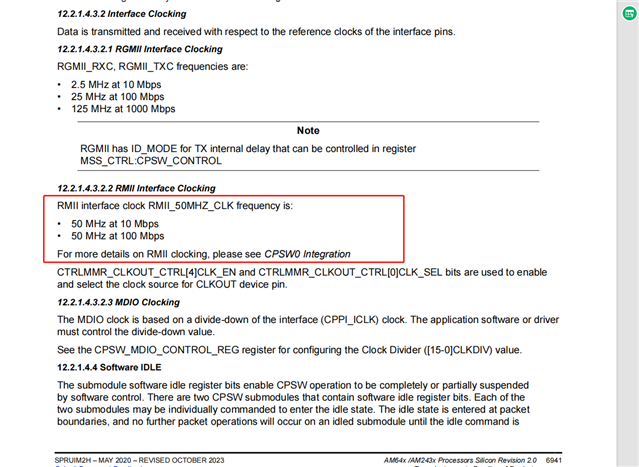

④在定制板中,RMII_CLK由 PHY提供50M时序给到AM6442的RMII_REF_CLK引脚。在TRM描述中50MHz的时钟输入,确实是有可能令RMII工作于10Mbps.如下图: