Part Number: TDA4VH-Q1

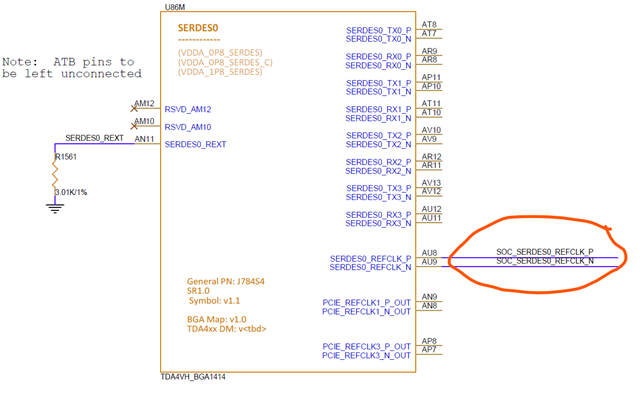

1,In the application of TDA4VH, if all serdes signals of serdes0 bank are not used, can the serdes0_REFCLK signal of this bank be left floating?

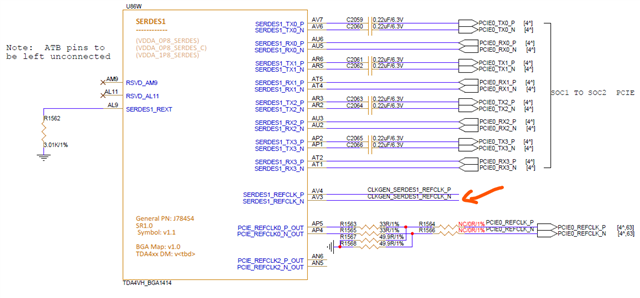

2,When serdes1 bank is used as the PCIE0 X4 RC mode, does the SERDES1_REFCLK signal still need to input a 100M clock? Can the PCIE_REFCLK0 signal directly output a 100M clock to the EP device as a reference clock?